US 20160111044A1

(19) **United States**

(12) **Patent Application Publication**

KISHI et al.

(10) **Pub. No.: US 2016/0111044 A1**

(43) **Pub. Date: Apr. 21, 2016**

(54) **DISPLAY DEVICE AND DRIVE METHOD FOR SAME**

(71) Applicant: **SHARP KABUSHIKI KAISHA**, Osaka (JP)

(72) Inventors: **Noritaka KISHI**, Osaka (JP); **Noboru NOGUCHI**, Osaka (JP); **Masanori OHARA**, Osaka (JP)

(21) Appl. No.: **14/787,793**

(22) PCT Filed: **Jun. 20, 2014**

(86) PCT No.: **PCT/JP2014/066403**

§ 371 (c)(1),

(2) Date: **Oct. 29, 2015**

(30) **Foreign Application Priority Data**

Jun. 27, 2013 (JP) ..... 2013-134638

**Publication Classification**

(51) **Int. Cl.**

**G09G 3/32**

(2006.01)

(52) **U.S. Cl.**

CPC ..... **G09G 3/3233** (2013.01); **G09G 2320/0626** (2013.01); **G09G 2320/0233** (2013.01); **G09G 2320/029** (2013.01); **G09G 2310/0291** (2013.01); **G09G 2320/041** (2013.01); **G09G 2330/021** (2013.01); **G09G 2300/0819** (2013.01); **G09G 2320/045** (2013.01)

(57) **ABSTRACT**

There is realized a display device capable of compensating for a deterioration of a circuit element while suppressing an increase of a circuit scale. One horizontal scanning period for a monitor row is composed of: a detection preparation period where preparation for detecting TFT characteristics and OLED characteristics is performed in the monitor row; a TFT characteristic detection period where current measurement for detecting the TFT characteristics is performed; an OLED characteristic detection period where current measurement for detecting the OLED characteristics is performed; and a light emission preparation period where preparation for allowing an organic EL element to emit light is performed in the monitor row. Data lines are used not only as signal lines that transfer a signal for allowing an organic EL element in each pixel circuit to emit light at desired brightness, but also as characteristic detecting signal lines.

Fig.1

Fig.2

Fig.3

Fig.4

Fig.5

Fig.6

Fig.7

Fig.8

|                | CHARACTERISTIC<br>DETECTION<br>OPERATION | USUAL<br>OPERATION                       |

|----------------|------------------------------------------|------------------------------------------|

| (K+1)-TH FRAME | FIRST ROW                                | SECOND TO n-TH ROW                       |

| (K+2)-TH FRAME | SECOND ROW                               | FIRST ROW, THIRD TO n-TH ROW             |

| (K+3)-TH FRAME | THIRD ROW                                | FIRST ROW, SECOND ROW, FORTH TO n-TH ROW |

| ⋮              | ⋮                                        | ⋮                                        |

| (K+n)-TH FRAME | n-TH ROW                                 | FIRST TO (n-1)-TH ROW                    |

Fig.9

Fig. 10

Fig.11

Fig.12

Fig.13

Fig. 14

Fig. 15

Fig. 16

Fig.17

Fig. 18

Fig.19

Fig.20

Fig.21

Fig.22

Fig. 23

Fig.24

Fig.25

Fig.26

Fig.27

Fig.28

Fig.29

Fig.30

|                  | OLED CHARACTERISTIC<br>DETECTION<br>OPERATION | TFT CHARACTERISTIC<br>DETECTION<br>OPERATION | USUAL<br>OPERATION                       |

|------------------|-----------------------------------------------|----------------------------------------------|------------------------------------------|

| (K+1)-TH FRAME   | FIRST ROW                                     |                                              | SECOND TO n-TH ROW                       |

| (K+2)-TH FRAME   | SECOND ROW                                    |                                              | FIRST ROW, THIRD TO n-TH ROW             |

| (K+3)-TH FRAME   | THIRD ROW                                     |                                              | FIRST ROW, SECOND ROW, FORTH TO n-TH ROW |

| ...              | ...                                           | ...                                          | ...                                      |

| (K+n)-TH FRAME   | n-TH ROW                                      |                                              | FIRST TO (n-1)-TH ROW                    |

| (K+n+1)-TH FRAME |                                               | FIRST ROW                                    | SECOND TO n-TH ROW                       |

| (K+n+2)-TH FRAME |                                               | SECOND ROW                                   | FIRST ROW, THIRD TO n-TH ROW             |

| (K+n+3)-TH FRAME |                                               | THIRD ROW                                    | FIRST ROW, SECOND ROW, FORTH TO n-TH ROW |

| ...              | ...                                           | ...                                          | ...                                      |

| (K+2n)-TH FRAME  |                                               | n-TH ROW                                     | FIRST TO (n-1)-TH ROW                    |

Fig.31

Fig. 32

Fig.33

Fig.34

Fig.35

Fig.36

Fig.37

Fig.38

Fig.39

Fig.40

## DISPLAY DEVICE AND DRIVE METHOD FOR SAME

### TECHNICAL FIELD

**[0001]** The present invention relates to a display device and a drive method for the same, and more specifically, relates to a display device including a pixel circuit having an electro-optical element such as an organic EL (Electro Luminescence) element, and to a drive method for the same.

### BACKGROUND ART

**[0002]** Heretofore, as a display element which the display device includes, there are: an electro-optical element in which brightness is controlled by a voltage applied thereto; and an electro-optical element in which brightness is controlled by a current flowing therethrough. As a representative example of the electro-optical element in which the brightness is controlled by the voltage applied thereto, a liquid crystal display element is mentioned. Meanwhile, as a representative example of the electro-optical element in which the brightness is controlled by the current flowing therethrough, an organic EL element is mentioned. The organic EL element is also referred to as an OLED (Organic Light-Emitting Diode). In comparison with the liquid crystal display device that requires a backlight, color filters and the like, an organic EL display device using the organic EL element that is a light emission-type electro-optical element can easily achieve thinning, reduction of electric power consumption, enhancement of the brightness, and the like. Hence, in recent years, development of the organic EL display device has been progressed positively.

**[0003]** As a drive method for the organic EL display device, a passive matrix method (also referred to as a simple matrix method) and an active matrix method are known. An organic EL display device that adopts the passive matrix method has a simple structure; however, a size increase and definition enhancement thereof are difficult. In contrast, an organic EL display device that adopts the active matrix method (hereinafter, referred to as an “active matrix-type organic EL display device”) can easily realize the size increase and the definition enhancement in comparison with the organic EL display device that adopts the passive matrix method.

**[0004]** In the active matrix-type organic EL display device, a plurality of pixel circuits is formed in a matrix fashion. Typically, each of the pixel circuits of the active matrix-type organic EL display device includes: an input transistor that selects a pixel; and a drive transistor that controls supply of a current to the organic EL element. Note that, in the following, the current flowing from the drive transistor to the organic EL element is sometimes referred to as a “drive current”.

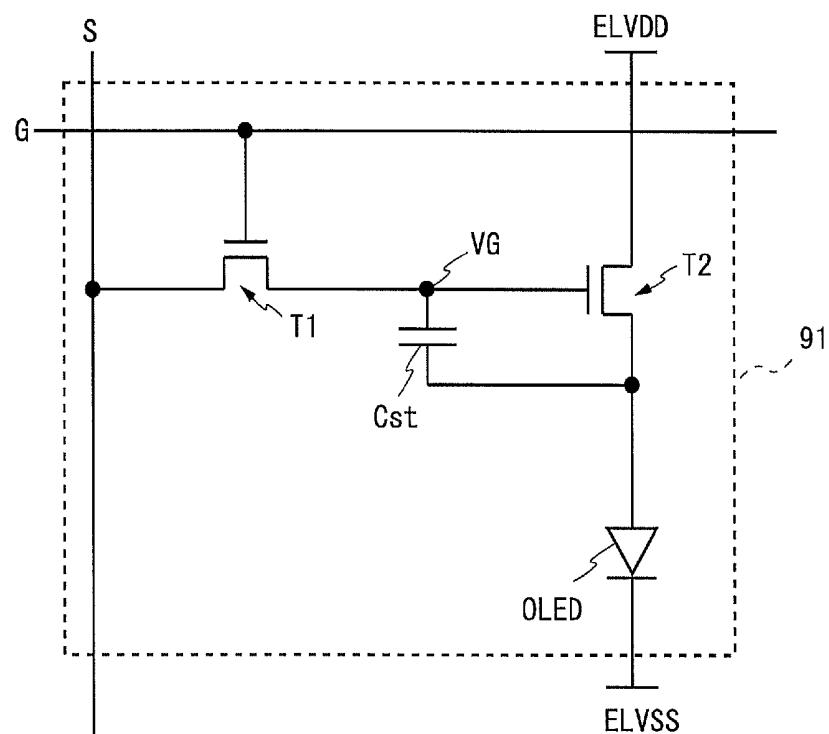

**[0005]** FIG. 37 is a circuit diagram showing a configuration of a conventional general pixel circuit 91. This pixel circuit 91 is provided so as to correspond to each of crossing points of a plurality of data lines S and a plurality of scanning lines G, which are arranged on a display unit. As shown in FIG. 37, this pixel circuit 91 includes: two transistors T1 and T2; one capacitor Cst; and one organic EL element OLED. The transistor T1 is an input transistor, and the transistor T2 is a drive transistor.

**[0006]** The transistor T1 is provided between the data line S and a gate terminal of the transistor T2. With regard to the transistor T1, a gate terminal thereof is connected to the scanning line G, and a source terminal thereof is connected to

the data line S. The transistor T2 is provided in series to the organic EL element OLED. With regard to the transistor T2, a drain terminal thereof is connected to a power supply line that supplies a high-level power supply voltage ELVDD, and a source terminal thereof is connected to an anode terminal of the organic EL element OLED. Note that the power supply line that supplies the high-level power supply voltage ELVDD is hereinafter referred to as a “high-level power supply line”, and the high-level power supply line is denoted by the same reference symbol ELVDD as that of the high-level power supply voltage. With regard to the capacitor Cst, one end thereof is connected to the gate terminal of the transistor T2, and other end thereof is connected to the source terminal of the transistor T2. A cathode terminal of the organic EL element OLED is connected to a power supply line that supplies a low-level power supply voltage ELVSS. Note that the power supply line that supplies the low-level power supply voltage ELVSS is hereinafter referred to as a “low-level power supply line”, and the low-level power supply line is denoted by the same reference symbol ELVSS as that of the low-level power supply voltage. Moreover, here, a connecting point of the gate terminal of the transistor T2, the one end of the capacitor Cst and the drain terminal of the transistor T1 is referred to as a “gate node VG” for the sake of convenience. Note that, in general, either one of the drain and the source, which has a higher potential, is referred to as the drain. However, in the explanation of this description, one thereof is defined as the drain, and the other thereof is defined as the source. Accordingly, in some case, a source potential becomes higher than a drain potential.

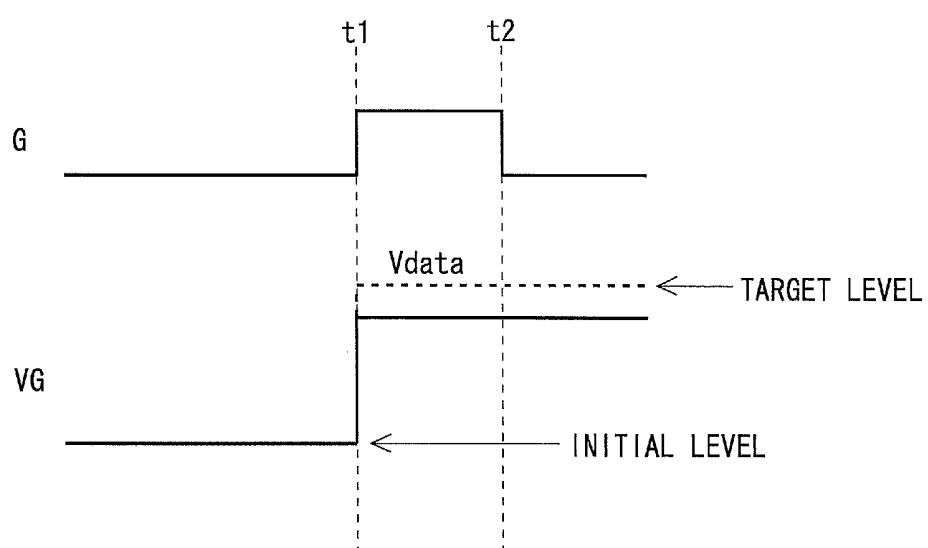

**[0007]** FIG. 38 is a timing chart for explaining operations of the pixel circuit 91 shown in FIG. 37. Before a time t1, the scanning line G is in a non-selection state. Hence, before the time t1, the transistor T1 is in an OFF state, and a potential of the gate node VG maintains an initial level (for example, a level corresponding to a write in an immediately previous frame). When the time t1 comes, the scanning line G turns to a selection state, and the transistor T1 turns ON. Thus, a data voltage Vdata corresponding to brightness of a pixel (sub-pixel), which is formed by this pixel circuit 91, is supplied to the gate node VG via the data line S and the transistor T1. Thereafter, during a period until a time t2, the potential of the gate node VG changes in response to the data voltage Vdata. At this time, the capacitor Cst is charged with a gate-source voltage Vgs that is a difference between the potential of the gate node Vg and the source potential of the transistor T2. When the time t2 comes, the scanning line G turns to the non-selection state. Thus, the transistor T1 turns OFF, and the gate-source voltage Vgs held by the capacitor Cst is determined. The transistor T2 supplies a drive current to the organic EL element OLED in response to the gate-source voltage Vgs held by the capacitor Cst. As a result, the organic EL element OLED emits light with brightness corresponding to the drive current.

**[0008]** Incidentally, in the organic EL display device, typically, a thin film transistor (TFT) is adopted as the drive transistor. However, the thin film transistor is prone to cause variations in a threshold voltage. When the variations of the threshold voltage occur in the drive transistor provided in the display unit, variations of the brightness occur, and accordingly, display quality is decreased. Accordingly, heretofore, there has been proposed a technology for suppressing the decrease of the display quality in the organic EL display device. For example, Japanese Patent Application Laid-Open

No. 2005-31630 discloses a technology for compensating the variations of the threshold voltage of the drive transistor. Moreover, Japanese Patent Application Laid-Open No. 2003-195810 and Japanese Patent Application Laid-Open No. 2007-128103 disclose a technology for constantly maintaining a current flowing from the pixel circuit to the organic EL element OLED. Furthermore, Japanese Patent Application Laid-Open No. 2007-233326 discloses a technology for displaying an image with uniform brightness irrespective of the threshold voltage and electron mobility of the drive transistor.

[0009] In accordance with the above-mentioned prior arts, even when the variations of the threshold voltage occur in the drive transistor provided in the display unit, it becomes possible to supply a constant current to the organic EL element (light-emitting element) in response to desired brightness (target brightness). However, with regard to the organic EL element, current efficiency thereof is decreased with the elapse of time. That is to say, even when the constant current is supplied to the organic EL element, the brightness is gradually decreased with the elapse of time. As a result, the burn-in occurs.

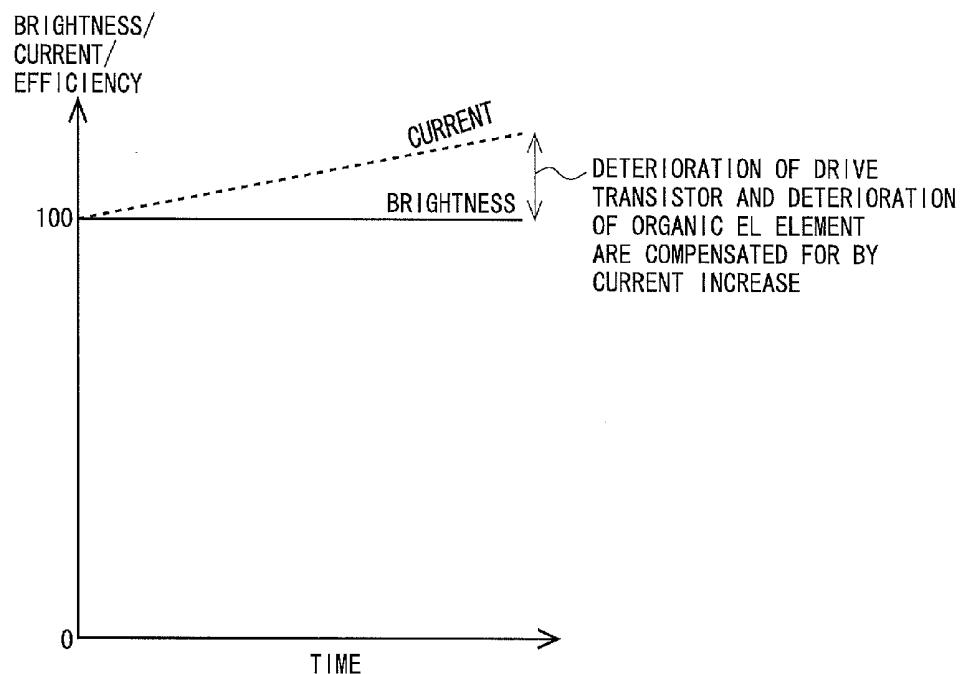

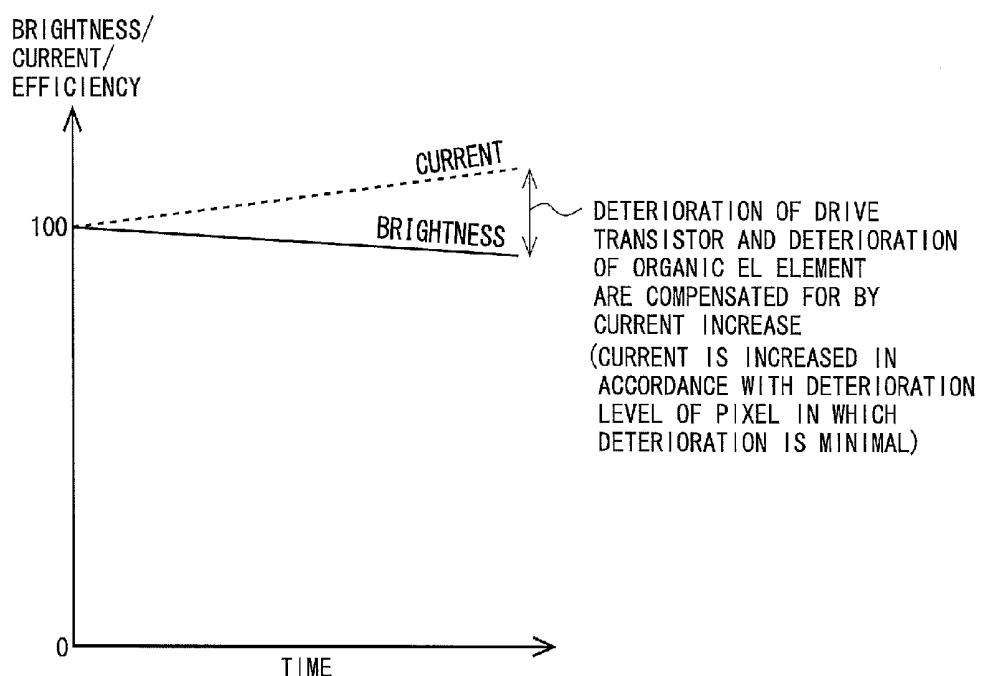

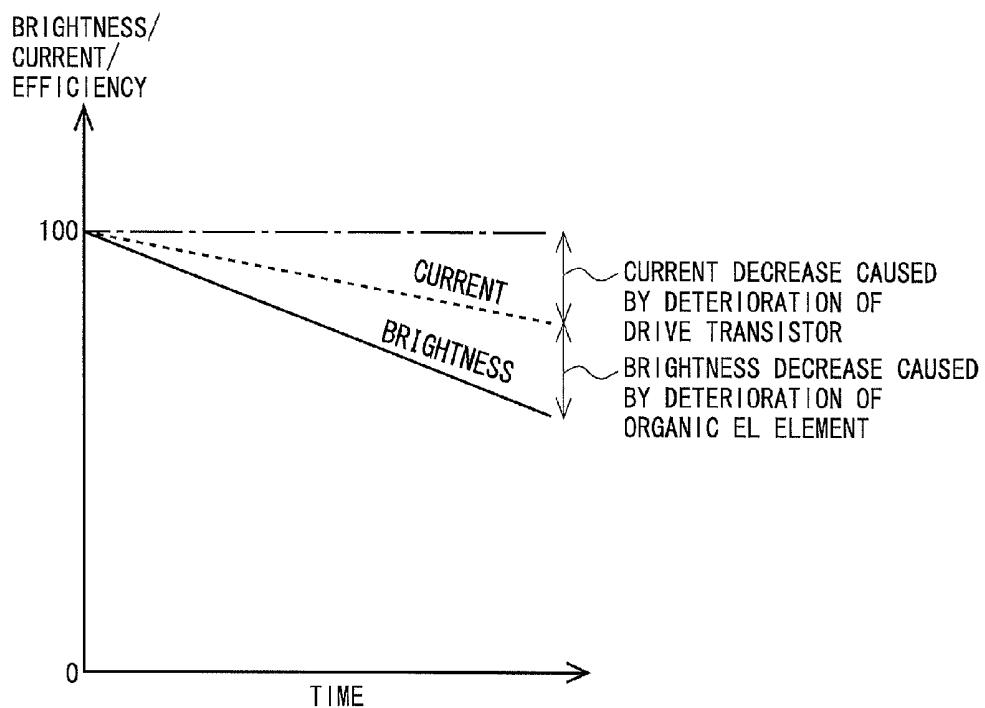

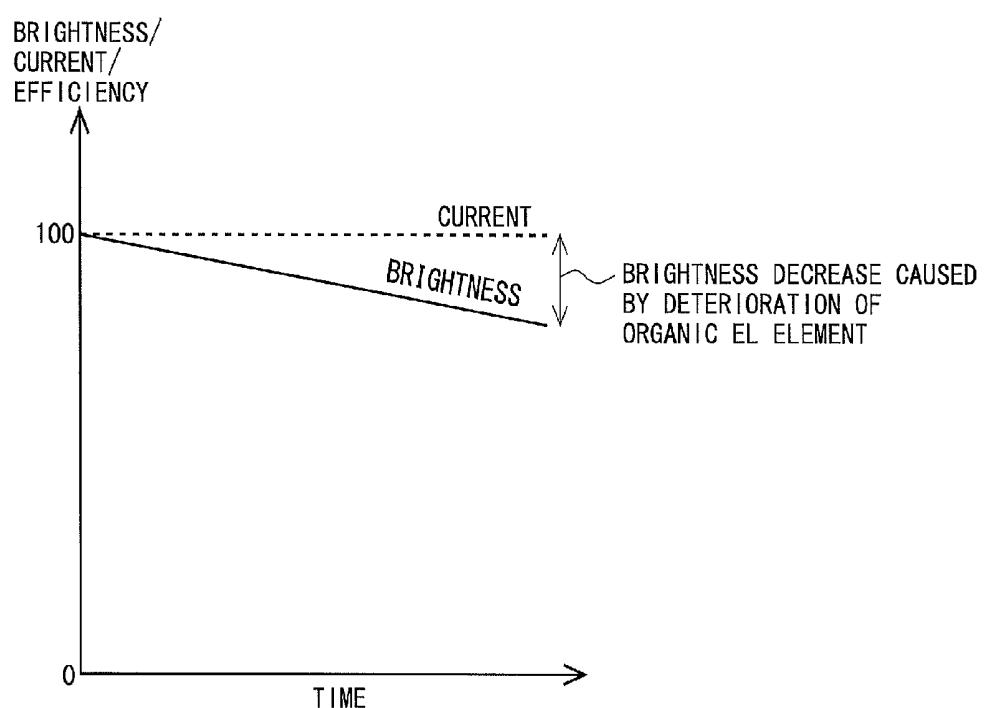

[0010] As stated above, if no compensation is made for such a deterioration of the drive transistor and such a deterioration of the organic EL element, then as shown in FIG. 39, a current decrease resulting from the deterioration of the drive transistor occurs, and in addition, a brightness decrease resulting from the deterioration of the organic EL element occurs. Moreover, even if the compensation is made for the deterioration of the drive transistor, the brightness decrease resulting from the deterioration of the organic EL element occurs as the time elapses as shown in FIG. 40. So, Japanese Unexamined Patent Application Publication No. 2008-523448 discloses a technology for making correction for data based on characteristics of the organic EL element OLED in addition to a technology for making correction for the data based on characteristics of the drive transistor.

#### PRIOR ART DOCUMENTS

##### Patent Documents

- [0011] [Patent Document 1] Japanese Patent Application Laid-Open No. 2005-31630

- [0012] [Patent Document 2] Japanese Patent Application Laid-Open No. 2003-195810

- [0013] [Patent Document 3] Japanese Patent Application Laid-Open No. 2007-128103

- [0014] [Patent Document 4] Japanese Patent Application Laid-Open No. 2007-233326

- [0015] [Patent Document 5] Japanese Unexamined Patent Application Publication No. 2008-523448

#### SUMMARY OF THE INVENTION

##### Problems to be Solved by the Invention

[0016] However, in accordance with the technology disclosed in Japanese Unexamined Patent Application Publication No. 2008-523448, only either one of the characteristics of the drive transistor and the characteristics of the organic EL element can be detected during a selection period. Therefore, the compensation cannot be made simultaneously for both of the deterioration of the drive transistor and the deterioration of the organic EL element. Moreover, it is necessary to elongate the selection period in order to detect the characteristics of both of the drive transistor and the organic EL element.

With regard to this, in the technology disclosed in Japanese Unexamined Patent Application Publication No. 2008-523448, in a case where such a selection period for a row for which the detection of the characteristics is performed is elongated, a duration of a light-emitting time differs between the row for which the detection of the characteristics is performed and other rows, and display with desired brightness is not performed. Moreover, in a case of attempting to configure the display device so as to make it possible to detect the characteristics of the drive transistor and the characteristics of the organic EL element, it is desired that a circuit scale should not be increased as much as possible. This is because the increase of the circuit scale brings a disadvantage, for example, in terms of achieving the reduction of the electric power consumption, miniaturization and the like.

[0017] In this connection, it is an object of the present invention to provide a display device capable of compensating for a deterioration of a circuit element while suppressing an increase of a circuit scale (in particular, a display device capable of simultaneously compensating for both of the deterioration of the drive transistor and the deterioration of the organic EL element).

#### Means for Solving the Problems

[0018] A first aspect of the present invention is directed to an active matrix-type display device comprising:

[0019] a display unit including: a pixel matrix of n rows and m columns (n and m are integers of 2 or more), which is composed of  $n \times m$  pieces of pixel circuits each including an electro-optical element in which brightness is controlled by a current and including a drive transistor for controlling a current to be supplied to the electro-optical element; scanning lines provided to correspond to respective rows of the pixel matrix; monitor control lines provided to correspond to the respective rows of the pixel matrix; and data lines provided to correspond to respective columns of the pixel matrix;

[0020] a pixel circuit drive unit configured to drive the scanning lines, the monitor control lines and the data lines so that characteristic detection processing for detecting characteristics of characteristic detection-target circuit elements including at least either of the electro-optical element and the drive transistor is performed in a frame period, and that each electro-optical element emits light in response to target brightness;

[0021] a correction data storage unit configured to store characteristic data, which are obtained based on results of the characteristic detection processing, as correction data for correcting video signals; and

[0022] a video signal correction unit configured to correct the video signals based on the correction data stored in the correction data storage unit, and to generate data signals to be supplied to the  $n \times m$  pieces of pixel circuits,

[0023] wherein each of the pixel circuits includes:

[0024] the electro-optical element;

[0025] an input transistor, in which a control terminal is connected to one of the scanning lines, a first conductive terminal is connected to one of the data lines, and a second conductive terminal is connected to the control terminal of the drive transistor;

[0026] a monitor control transistor, in which a control terminal is connected to one of the monitor control lines, a first conductive terminal is connected to the second conductive terminal of the drive transistor and to the

anode of the electro-optical element, and a second conductive terminal is connected to one of the data lines;

[0027] the drive transistor in which a first conductive terminal is given a drive power supply potential; and

[0028] a first capacitor in which one end is connected to a control terminal of the drive transistor in order to hold a potential of the control terminal of the drive transistor,

[0029] wherein, when a row in which the characteristic detection processing is performed in the frame period is defined as a monitor row, and each of rows other than the monitor row is defined as a non-monitor row, the frame period includes a characteristic detection processing period composed of: a detection preparation period where a preparation for detecting characteristics of the characteristic detection-target circuit elements is performed in the monitor row; a current measurement period where the characteristics of the characteristic detection-target circuit elements are detected by measuring currents flowing through the data lines; and a light emission preparation period where a preparation for allowing the electro-optical element to emit light is performed in the monitor row,

[0030] the pixel circuit drive unit drives the scanning lines so that the input transistor becomes an ON state during the detection preparation period and the light emission preparation period, and that the input transistor becomes an OFF state during the current measurement period,

[0031] the pixel circuit drive unit drives the monitor control lines so that the monitor control transistor becomes an OFF state during the detection preparation period and the light emission preparation period, and that the monitor control transistor becomes an ON state during the current measurement period,

[0032] the pixel circuit drive unit gives the data lines a first predetermined potential during the detection preparation period, the first predetermined potential being determined based on the characteristics of the electro-optical element and the characteristics of the drive transistor,

[0033] the pixel circuit drive unit gives the data lines a second predetermined potential during the current measurement period, the second predetermined potential serving for allowing a current in accordance with the characteristics of each of the characteristic detection-target circuit elements to flow through each of the data lines, and

[0034] the pixel circuit drive unit gives the data lines a potential in accordance with a target brightness of the electro-optical element during the light emission preparation period.

[0035] According to a second aspect of the present invention, in the first aspect of the present invention,

[0036] the pixel circuit drive unit includes output and current-monitor circuits having a function to apply the data signals to the data lines, and a function to measure the currents flowing through the data lines,

[0037] each of the output and current-monitor circuits includes:

[0038] an operational amplifier, in which a non-inverting input terminal is given one of the data signals, and an inverting input terminal is connected to one of the data lines;

[0039] a second capacitor, in which one end is connected to one of the data lines, and other end is connected to an output terminal of the operational amplifier; and

[0040] a switch, in which one end is connected to one of the data lines, and other end is connected to the output terminal of the operational amplifier, and

[0041] each of the output and current-monitor circuits measure currents flowing through the data lines by allowing the switch to be turned to OFF state after giving the data lines the second predetermined potential by allowing the switch to be turned to ON state, in the current measurement period.

[0042] According to a third aspect of the present invention, in the second aspect of the present invention,

[0043] one output and current-monitor circuit is provided for a plurality of the data lines, and

[0044] the plurality of data lines are electrically connected sequentially to the output and current-monitor circuits every predetermined period.

[0045] According to a fourth aspect of the present invention, in the first aspect of the present invention,

[0046] the characteristic detection processing period is provided in a vertical scanning period.

[0047] According to a fifth aspect of the present invention, in the fourth aspect of the present invention,

[0048] when any electro-optical element is defined as a focus-target electro-optical element, in a case where the focus-target electro-optical element is included in the monitor row, the pixel circuit drive unit gives the data lines a potential of a data signal during the light emission preparation period, the potential being equivalent to a gradation voltage larger than a gradation voltage in a case where the focus-target electro-optical element is included in the non-monitor row.

[0049] According to a sixth aspect of the present invention, in the first aspect of the present invention,

[0050] the characteristic detection processing period is provided in a vertical retrace line period.

[0051] According to a seventh aspect of the present invention, in the sixth aspect of the present invention,

[0052] when any electro-optical element is defined as a focus-target electro-optical element, in a case where the focus-target electro-optical element is included in the monitor row, the pixel circuit drive unit gives the data lines a potential of a data signal in an event of performing writing of the data signals to pixel circuits included in the monitor row in a vertical scanning period, the potential being equivalent to a gradation voltage larger than a gradation voltage in a case where the focus-target electro-optical element is included in the non-monitor row.

[0053] According to an eighth aspect of the present invention, in the first aspect of the present invention,

[0054] the characteristic detection processing is performed for only one row of the pixel matrix for one frame period.

[0055] According to a ninth aspect of the present invention, in the first aspect of the present invention,

[0056] there are: a frame in which detection of the characteristics of only the drive transistor as the characteristic detection-target circuit elements is performed; and a frame in which detection of the characteristics of only the electro-optical element as the characteristic detection-target circuit elements is performed.

[0057] According to a tenth aspect of the present invention, in the first aspect of the present invention,

[0058] the current measurement period is composed of: a drive transistor characteristic detection period where a current measurement for detecting the characteristics of the drive transistor is performed; and an electro-optical element char-

acteristic detection period where a current measurement for detecting the characteristics of the electro-optical element is performed, and

[0059] the pixel circuit drive unit gives the data lines different potentials between the drive transistor characteristic detection period and the electro-optical element characteristic detection period, as the second predetermined potential.

[0060] According to an eleventh aspect of the present invention, in the tenth aspect of the present invention,

[0061] when a potential given to one of the data lines in the detection preparation period is defined as  $V_{mg}$ , a potential given to one of the data lines in the drive transistor characteristic detection period is defined as  $V_{m\_TFT}$ , and a potential given to one of the data lines in the electro-optical element characteristic detection period is defined as  $V_{m\_oled}$ , a value of  $V_{mg}$  is determined to satisfy following expressions:

$$V_{mg} > V_{m\_TFT} + V_{th}(T2)$$

$$V_{mg} < V_{m\_oled} + V_{th}(T2)$$

where  $V_{th}(T2)$  is a threshold voltage of the drive transistor.

[0062] According to a twelfth aspect of the present invention, in the tenth aspect of the present invention,

[0063] when a potential given to one of the data lines in the detection preparation period is defined as  $V_{mg}$ , and a potential given to one of the data lines in the drive transistor characteristic detection period is defined as  $V_{m\_TFT}$ , a value of  $V_{m\_TFT}$  is determined to satisfy following expressions:

$$V_{m\_TFT} < V_{mg} - V_{th}(T2)$$

$$V_{m\_TFT} < ELVSS + V_{th}(\text{oled})$$

where  $V_{th}(T2)$  is a threshold voltage of the drive transistor,  $V_{th}(\text{oled})$  is a light emission threshold voltage of the electro-optical element, and  $ELVSS$  is a potential of a cathode of the electro-optical element.

[0064] According to a thirteenth aspect of the present invention, in the tenth aspect of the present invention,

[0065] when a potential given to one of the data lines in the detection preparation period is defined as  $V_{mg}$ , and a potential given to one of the data lines in the electro-optical element characteristic detection period is defined as  $V_{m\_oled}$ , a value of  $V_{m\_oled}$  is determined to satisfy following expressions:

$$V_{m\_oled} > V_{mg} - V_{th}(T2)$$

$$V_{m\_oled} > ELVSS + V_{th}(\text{oled})$$

where  $V_{th}(T2)$  is a threshold voltage of the drive transistor,  $V_{th}(\text{oled})$  is a light emission threshold voltage of the electro-optical element, and  $ELVSS$  is a potential of a cathode of the electro-optical element.

[0066] According to a fourteenth aspect of the present invention, in the tenth aspect of the present invention,

[0067] when a potential given to one of the data lines in the detection preparation period is defined as  $V_{mg}$ , a potential given to one of the data lines in the drive transistor characteristic detection period is defined as  $V_{m\_TFT}$ , and a potential given to one of the data lines in the electro-optical element characteristic detection period is defined as  $V_{m\_oled}$ , values of  $V_{mg}$ ,  $V_{m\_TFT}$  and  $V_{m\_oled}$  are determined to satisfy following relationships:

$$V_{m\_TFT} < V_{mg} - V_{th}(T2)$$

$$V_{m\_TFT} < ELVSS + V_{th}(\text{oled})$$

$$V_{m\_oled} > V_{mg} - V_{th}(T2)$$

$$V_{m\_oled} > ELVSS + V_{th}(\text{oled})$$

where  $V_{th}(T2)$  is a threshold voltage of the drive transistor,  $V_{th}(\text{oled})$  is a light emission threshold voltage of the electro-optical element, and  $ELVSS$  is a potential of a cathode of the electro-optical element.

[0068] According to a fifteenth aspect of the present invention, in the first aspect of the present invention,

[0069] the display device further comprises:

[0070] a temperature detection unit configured to detect a temperature; and

[0071] a temperature change compensation unit configured to implement, for the characteristic data, a correction that is based on the temperature detected by the temperature detection unit,

[0072] wherein data subjected to the correction by the temperature change compensation unit is stored as the correction data in the correction data storage unit.

[0073] According to a sixteenth aspect of the present invention, in the first aspect of the present invention,

[0074] the display device further comprises a monitor region storage unit configured to store information for identifying a region where the characteristic detection processing is performed last in an event where a power supply is turned OFF,

[0075] wherein, after the power supply is turned ON, the characteristic detection processing is performed from a region in a vicinity of a region obtained based on information stored in the monitor region storage unit.

[0076] A seventeenth aspect of the present invention is directed to a drive method of a display device including: a pixel matrix of  $n$  rows and  $m$  columns ( $n$  and  $m$  are integers of 2 or more), which is composed of  $n \times m$  pieces of pixel circuits each including an electro-optical element in which brightness is controlled by a current and including a drive transistor for controlling a current to be supplied to the electro-optical element; scanning lines provided to correspond to respective rows of the pixel matrix; monitor control lines provided to correspond to the respective rows of the pixel matrix; and data lines provided to correspond to respective columns of the pixel matrix, the drive method comprising:

[0077] a pixel circuit driving step of driving the scanning lines, the monitor control lines and the data lines so that characteristic detection processing for detecting characteristics of characteristic detection-target circuit elements including at least either of the electro-optical element and the drive transistor is performed in a frame period, and that each electro-optical element emits light in response to target brightness;

[0078] a correction data storing step of storing characteristic data, which are obtained based on results of the characteristic detection processing, as correction data for correcting video signals, in a correction data storage unit prepared in advance; and

[0079] a video signal correction step of correcting the video signals based on the correction data stored in the correction data storage unit, and generating data signals to be supplied to the  $n \times m$  pieces of pixel circuits,

[0080] wherein each of the pixel circuits includes:

[0081] the electro-optical element;

[0082] an input transistor, in which a control terminal is connected to one of the scanning lines, a first conductive terminal is connected to one of the data lines, and a

second conductive terminal is connected to the control terminal of the drive transistor; a monitor control transistor, in which a control terminal is connected to one of the monitor control lines, a first conductive terminal is connected to the second conductive terminal of the drive transistor and to the anode of the electro-optical element, and a second conductive terminal is connected to one of the data lines;

[0083] the drive transistor in which a first conductive terminal is given a drive power supply potential; and

[0084] a first capacitor in which one end is connected to a control terminal of the drive transistor in order to hold a potential of the control terminal of the drive transistor,

[0085] wherein, when a row in which the characteristic detection processing is performed in the frame period is defined as a monitor row, and each of rows other than the monitor row is defined as a non-monitor row, the frame period includes a characteristic detection processing period composed of: a detection preparation period where a preparation for detecting characteristics of the characteristic detection-target circuit elements is performed in the monitor row; a current measurement period where the characteristics of the characteristic detection-target circuit elements are detected by measuring currents flowing through the data lines; and a light emission preparation period where a preparation for allowing the electro-optical element to emit light is performed in the monitor row,

[0086] in the pixel circuit driving step,

[0087] the scanning lines are driven so that the input transistor becomes an ON state during the detection preparation period and the light emission preparation period, and that the input transistor becomes an OFF state during the current measurement period,

[0088] the monitor control lines are driven so that the monitor control transistor becomes an OFF state during the detection preparation period and the light emission preparation period, and that the monitor control transistor becomes an ON state during the current measurement period,

[0089] the data lines are given a first predetermined potential during the detection preparation period, the first predetermined potential being determined based on the characteristics of the electro-optical element and the characteristics of the drive transistor,

[0090] the data lines are given a second predetermined potential during the current measurement period, the second predetermined potential serving for allowing a current in accordance with the characteristics of each of the characteristic detection-target circuit elements to flow through each of the data lines, and

[0091] the data lines are given a potential in accordance with a target brightness of the electro-optical element during the light emission preparation period.

#### Effects of the Invention

[0092] According to the first aspect of the present invention, in a display device that has the pixel circuits, each including the electro-optical element (for example, an organic EL element) in which the brightness is controlled by the current, and including the drive transistor for controlling the current to be supplied to the electro-optical element, the characteristics of the circuit elements (at least either one of the electro-optical element and the drive transistor) are detected in the frame period. Then, the video signals are

corrected by using the correction data obtained in consideration of a result of the detection. The data signals which are based on the video signals thus corrected are supplied to the pixel circuits, and accordingly, a drive current with such a magnitude that compensates for the deterioration of the circuit elements is supplied to the electro-optical element. Here, the characteristics of the circuit elements are detected by measuring the currents flowing through the data lines. That is to say, the data lines are not only used as signal lines which transfer signals for allowing the electro-optical elements in the respective pixel circuits to emit light at desired brightness, but are also used as characteristic detecting signal lines. Therefore, it is not necessary to provide new signal lines in the display unit in order to detect the characteristics of the circuit elements. Hence, it becomes possible to compensate for the deterioration of the circuit elements while suppressing the increase of the circuit scale.

[0093] According to the second aspect of the present invention, without complicating the configuration of the pixel circuit drive unit, it becomes possible to use the data lines as the characteristic detecting signal lines as well as the signal lines which transfer the signals for allowing the electro-optical elements in the respective pixel circuits to emit light at the desired brightness.

[0094] According to the third aspect of the present invention, in the display device adopting the source share driving (SSD) method, it becomes possible to compensate for the deterioration of the circuit elements while suppressing the increase of the circuit scale.

[0095] According to the fourth aspect of the present invention, unlike the configuration in which the characteristic detection processing period is provided in the vertical retrace line period, it is sufficient to perform the writing in the monitor row, which corresponds to the target brightness, only once for a frame period.

[0096] According to the fifth aspect of the present invention, the potential of each of the data signals is adjusted in consideration that a length of the light emission period of the electro-optical element in the monitor row becomes shorter than a length of the light emission period of the electro-optical element in the non-monitor row. Therefore, the decrease of the display quality is suppressed.

[0097] According to the sixth aspect of the present invention, for the monitor row, after the writing in the vertical scanning period, the writing is performed one more time in the light emission preparation period during the vertical retrace line period. With regard to this, in order that the writing in the light emission preparation period can be enabled, it is necessary to hold the corresponding data after the writing in the vertical scanning period. With regard to this, the data to be held is no more than data equivalent to one line, and accordingly, an increase of a memory capacity is slight. In contrast, in the configuration in which the characteristic detection processing period is provided in the vertical scanning period, a line memory equivalent to several ten lines are sometimes required. Accordingly, a required memory capacity is reduced in comparison with the configuration in which the characteristic detection processing period is provided in the vertical scanning period.

[0098] According to the seventh aspect of the present invention, the potential of each of the data signals is adjusted in consideration that the electro-optical element is tempo-

rarily turned OFF in the vertical retrace line period in the monitor row. Therefore, the decrease of the display quality is suppressed.

[0099] According to the eighth aspect of the present invention, it is sufficient to include the characteristic detection processing period for only one row in the frame period. Therefore, a vertical retrace line period with a sufficient length for the frame period is ensured.

[0100] According to the ninth aspect of the present invention, it is sufficient to include the characteristic detection processing period for detecting either one of the characteristics of the electro-optical element and the characteristics of the drive transistor in the frame period. Therefore, a vertical retrace line period with a sufficient length for the frame period is ensured.

[0101] According to the tenth aspect of the present invention, the characteristics of the electro-optical element and the drive transistor are detected in the frame period. Therefore, it becomes possible to compensate for both of the deterioration of the electro-optical element and the deterioration of the drive transistor while suppressing the increase of the circuit scale.

[0102] According to the eleventh aspect of the present invention, the drive transistor surely turns to the ON state in the drive transistor characteristic detection period, and the electro-optical element surely turns to the ON state in the electro-optical element characteristic detection period.

[0103] According to the twelfth aspect of the present invention, in the drive transistor characteristic detection period, the drive transistor surely turns to the ON state, and in addition, the electro-optical element surely turns to the OFF state.

[0104] According to the thirteenth aspect of the present invention, in the electro-optical element characteristic detection period, the drive transistor surely turns to the OFF state, and in addition, the electro-optical element surely turns to the ON state.

[0105] According to the fourteenth aspect of the present invention, in the drive transistor characteristic detection period, the drive transistor surely turns to the ON state, and in addition, the electro-optical element surely turns to the OFF state. Moreover, in the electro-optical element characteristic detection period, the drive transistor surely turns to the OFF state, and in addition, the electro-optical element surely turns to the ON state.

[0106] According to the fifteenth aspect of the present invention, the video signals are corrected by using the correction data in which the temperature change is taken into consideration. Therefore, it becomes possible to compensate for both of the deterioration of the drive transistor and the deterioration of the electro-optical element irrespective of the change of the temperature.

[0107] According to the sixteenth aspect of the present invention, a difference in number of detection times of the characteristics of the characteristic detection-target circuit element is prevented from occurring between the upper rows and the lower rows. Therefore, it becomes possible to perform the compensation, which is made for the deterioration of such characteristic detection-target circuit elements, uniformly on the entire screen, and the occurrence of the brightness variations is prevented effectively.

[0108] According to the seventeenth aspect of the present invention, similar effects to those of the first aspect of the present invention can be exerted in the invention of the drive method for the display device.

#### BRIEF DESCRIPTION OF THE DRAWINGS

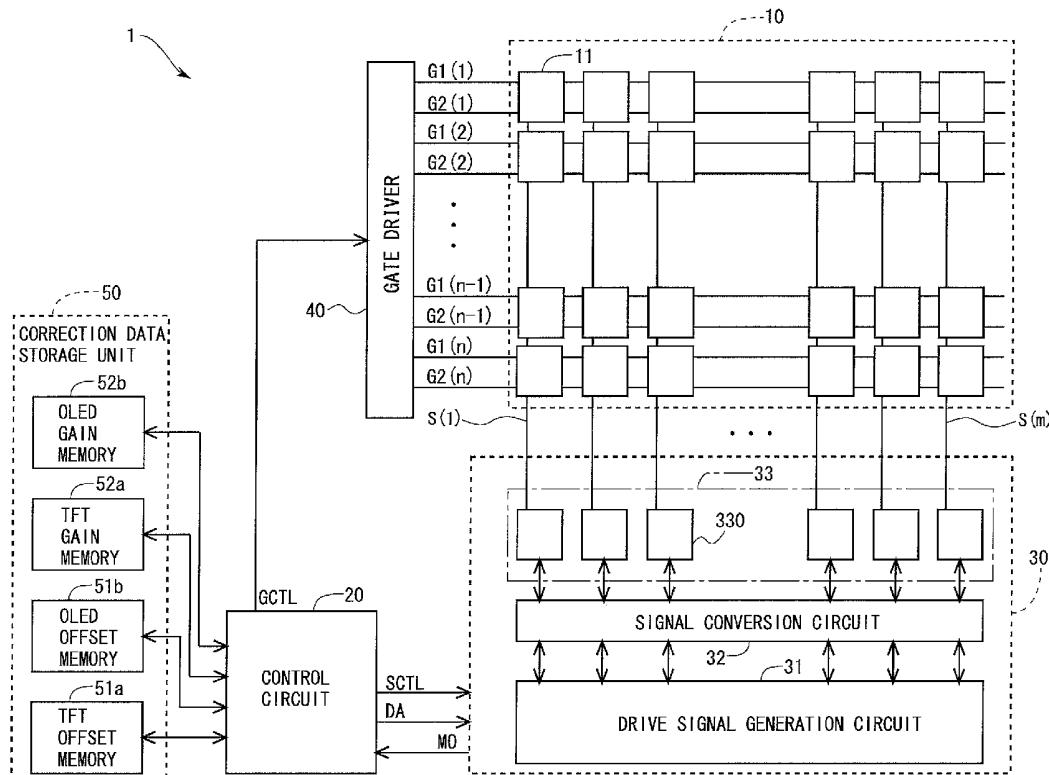

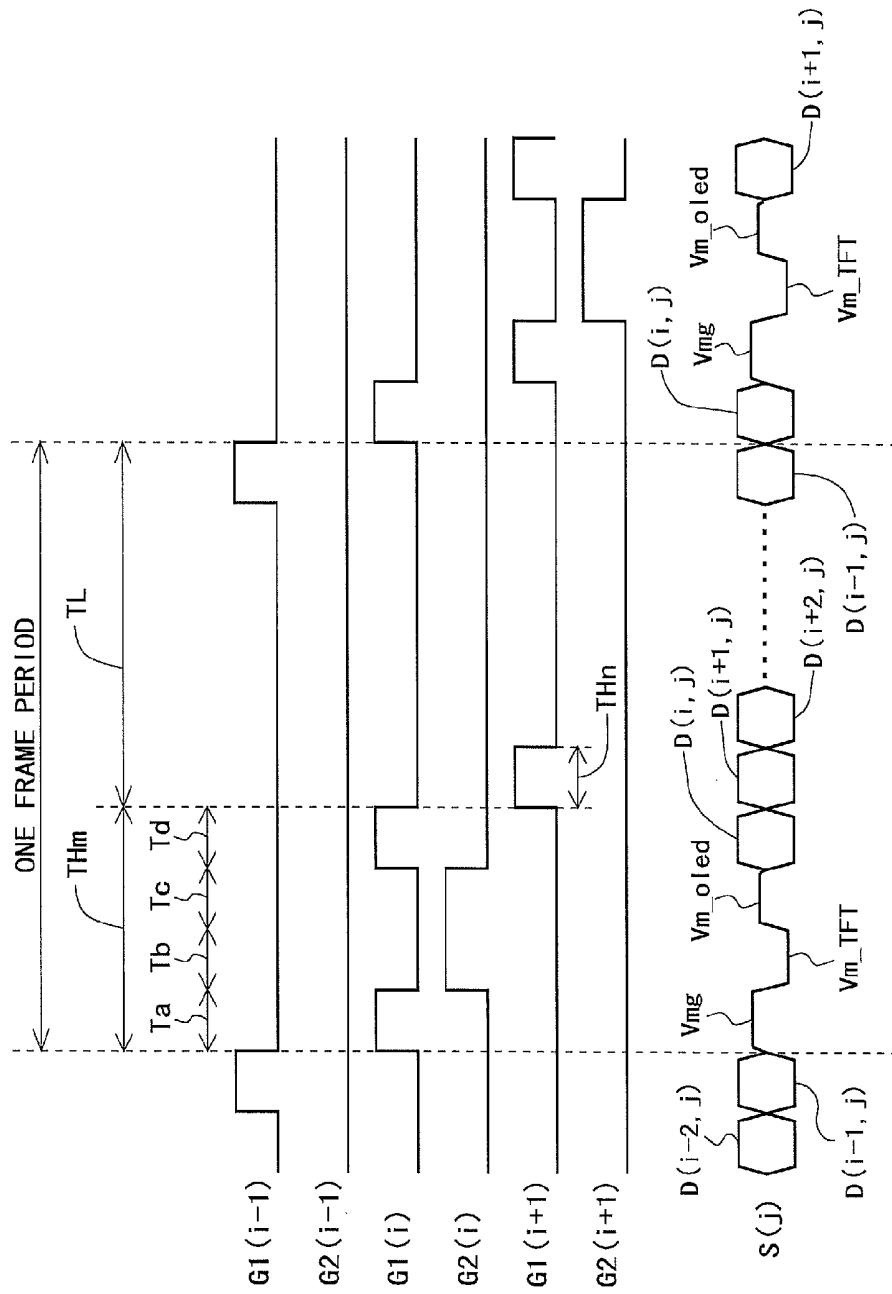

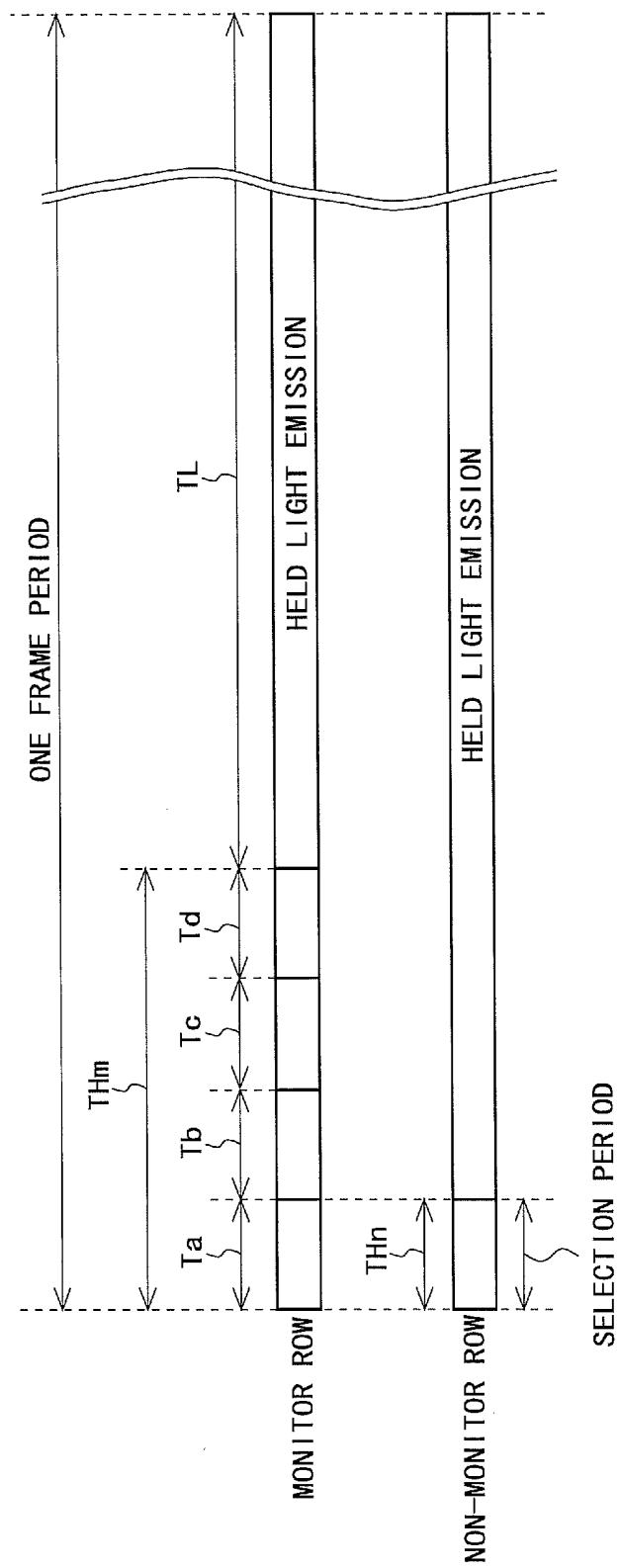

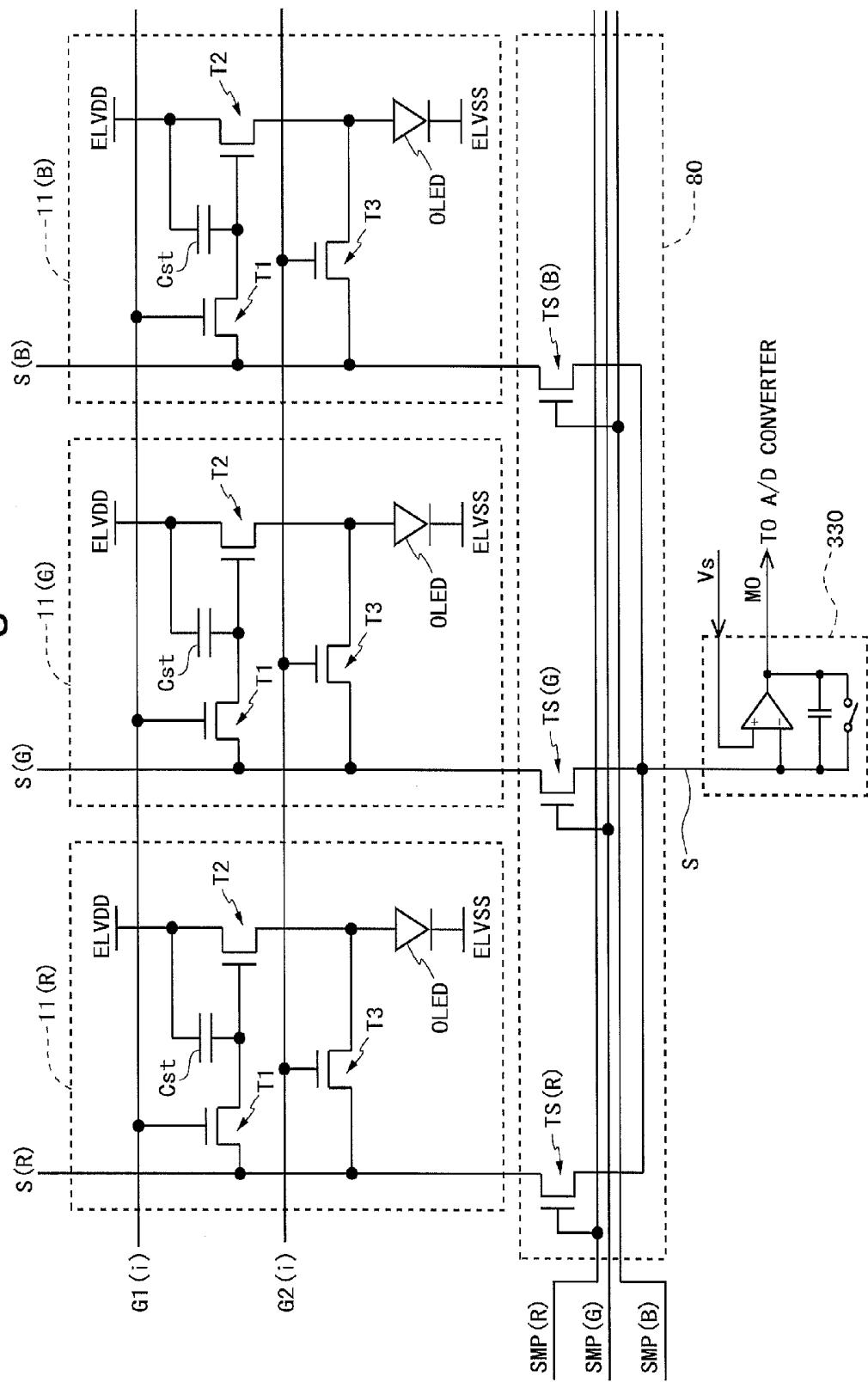

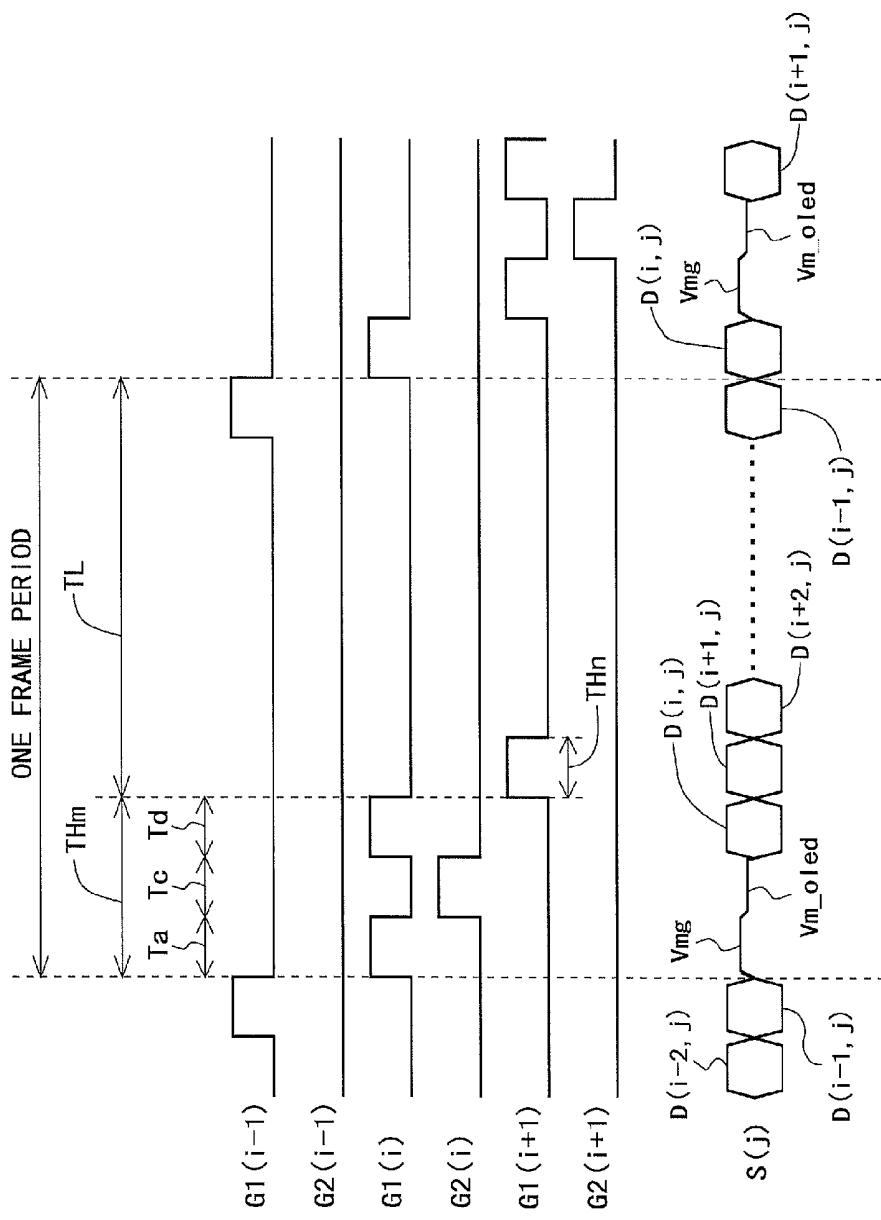

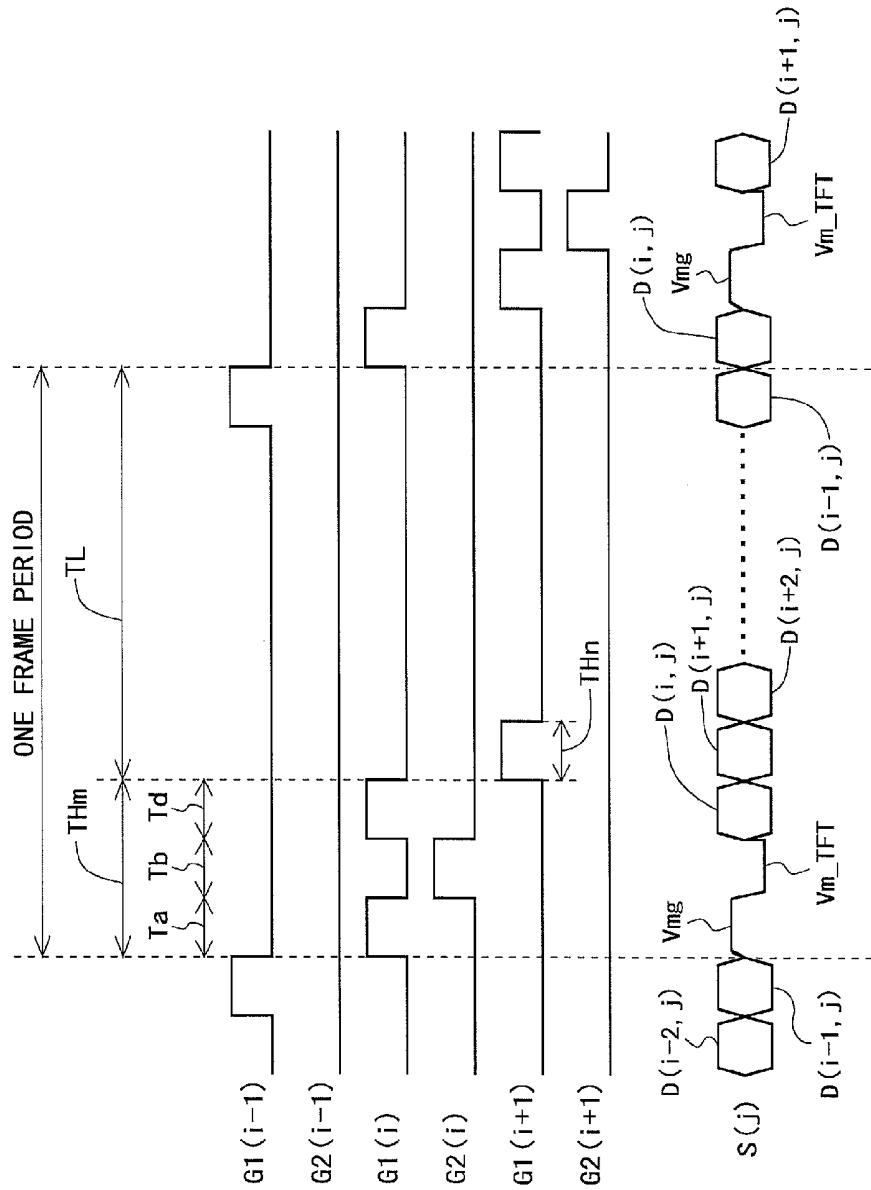

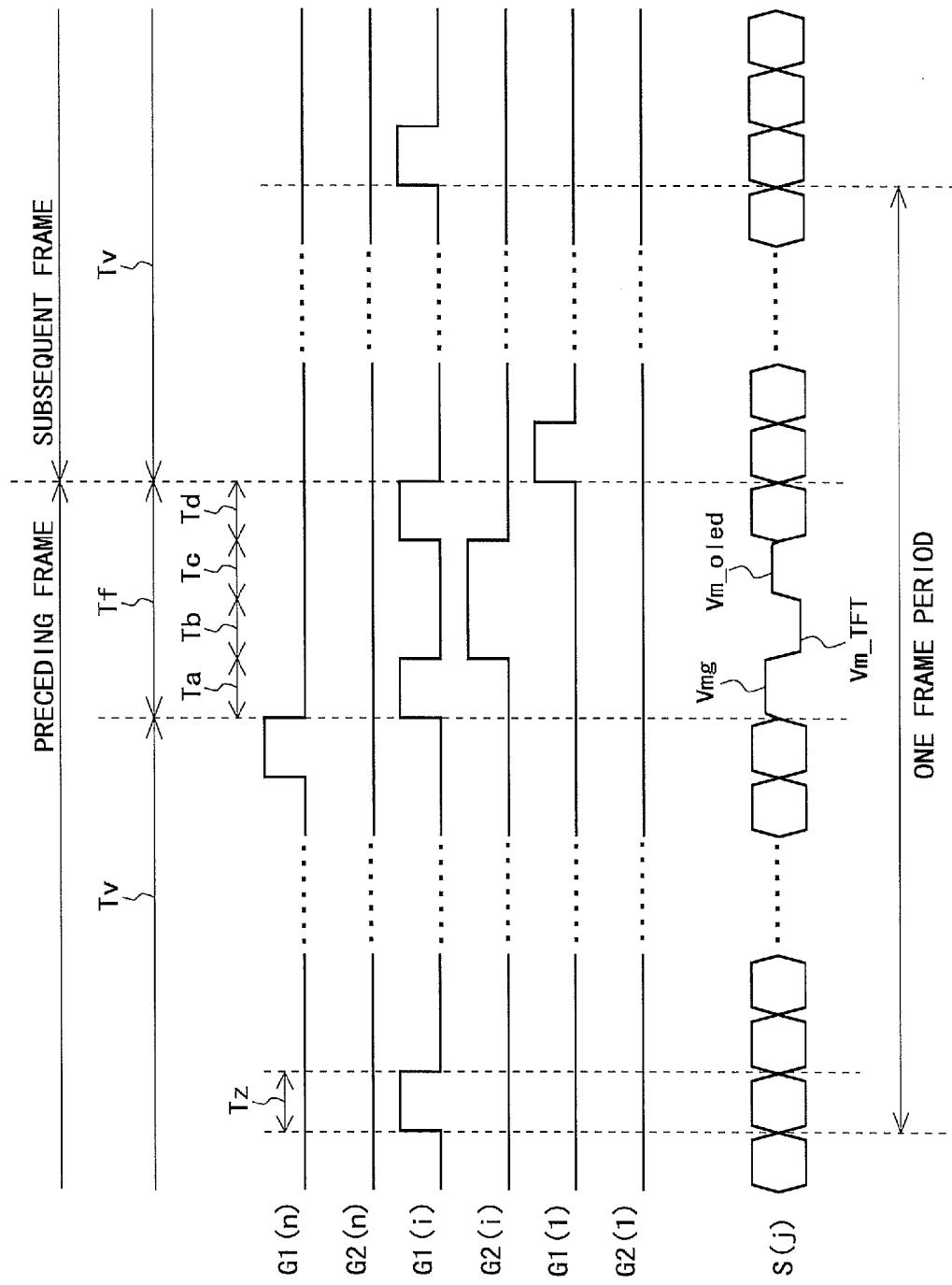

[0109] FIG. 1 is a timing chart for explaining details of one horizontal scanning period for a monitor row in an embodiment of the present invention.

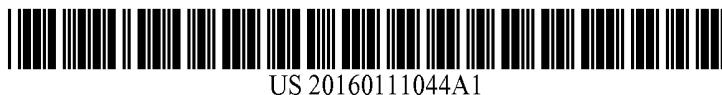

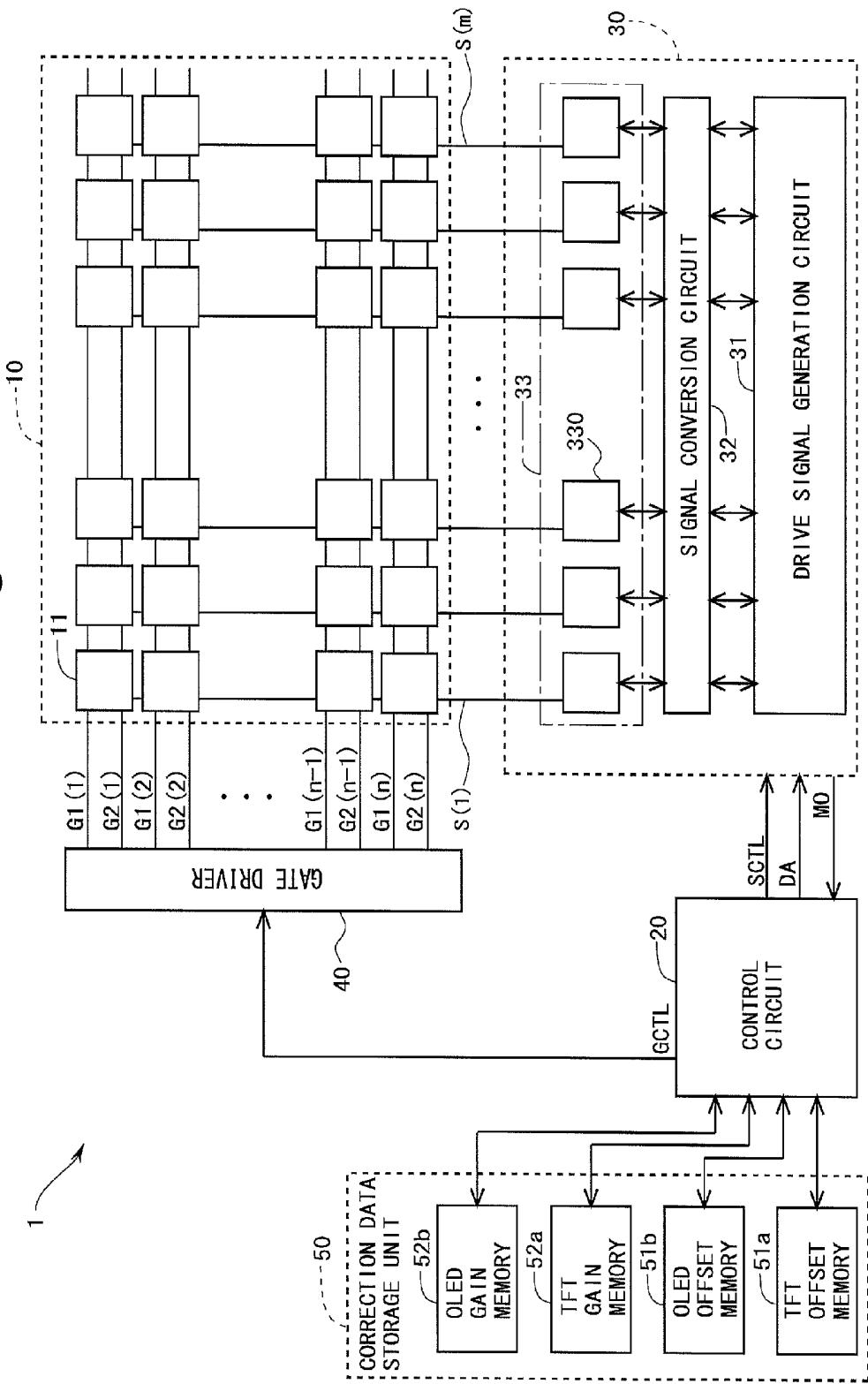

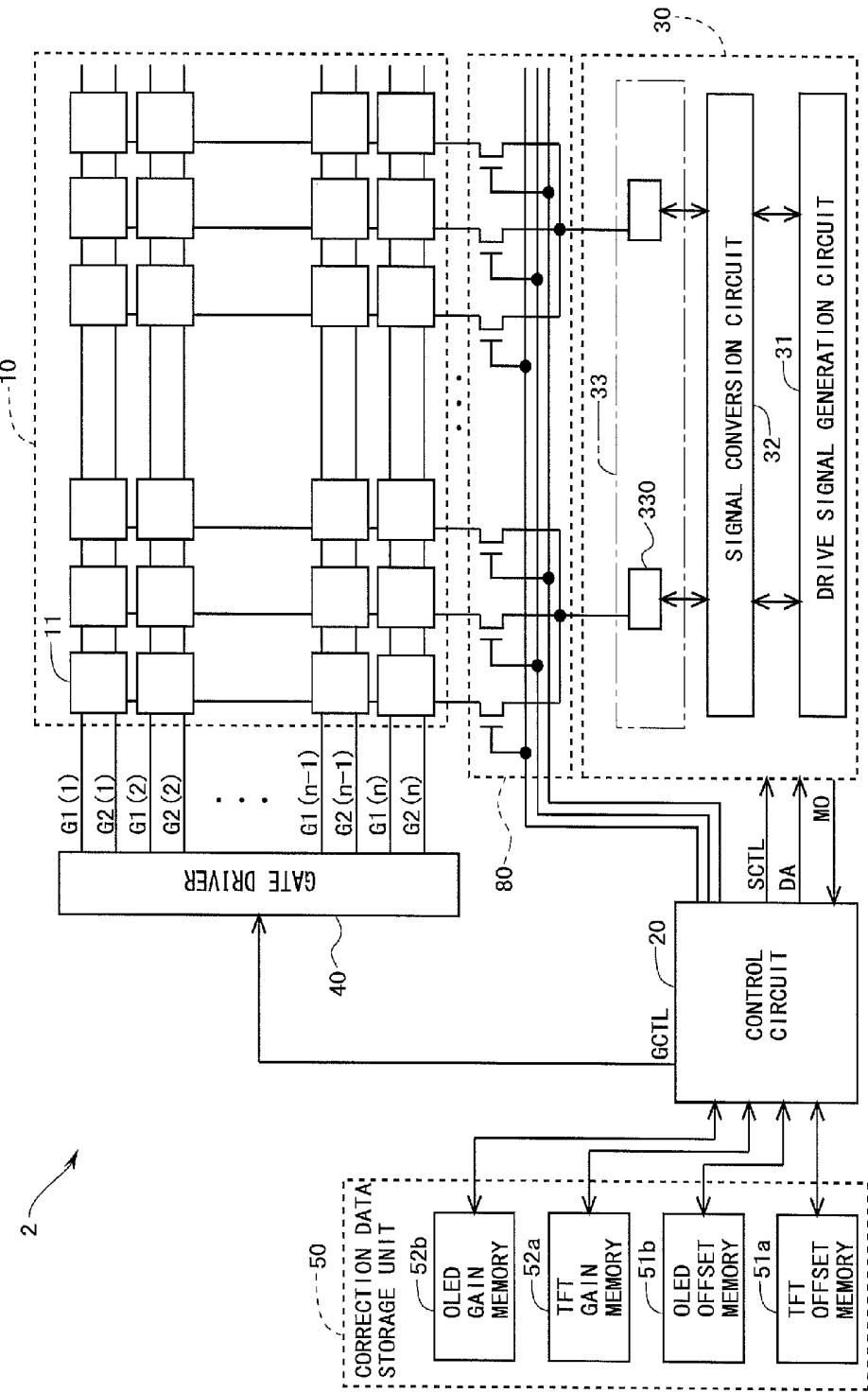

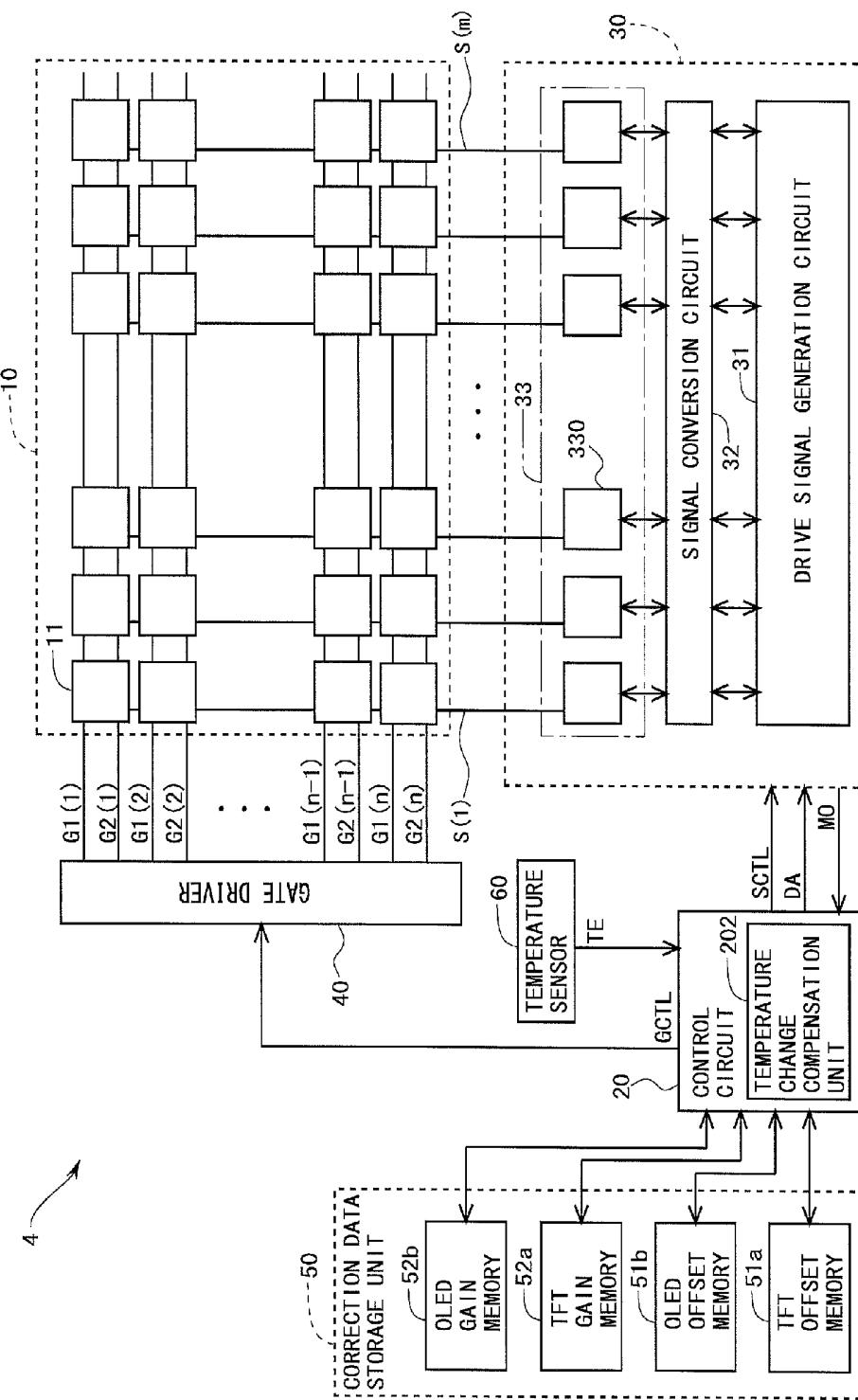

[0110] FIG. 2 is a block diagram showing an overall configuration of an active matrix-type organic EL display device according to the embodiment.

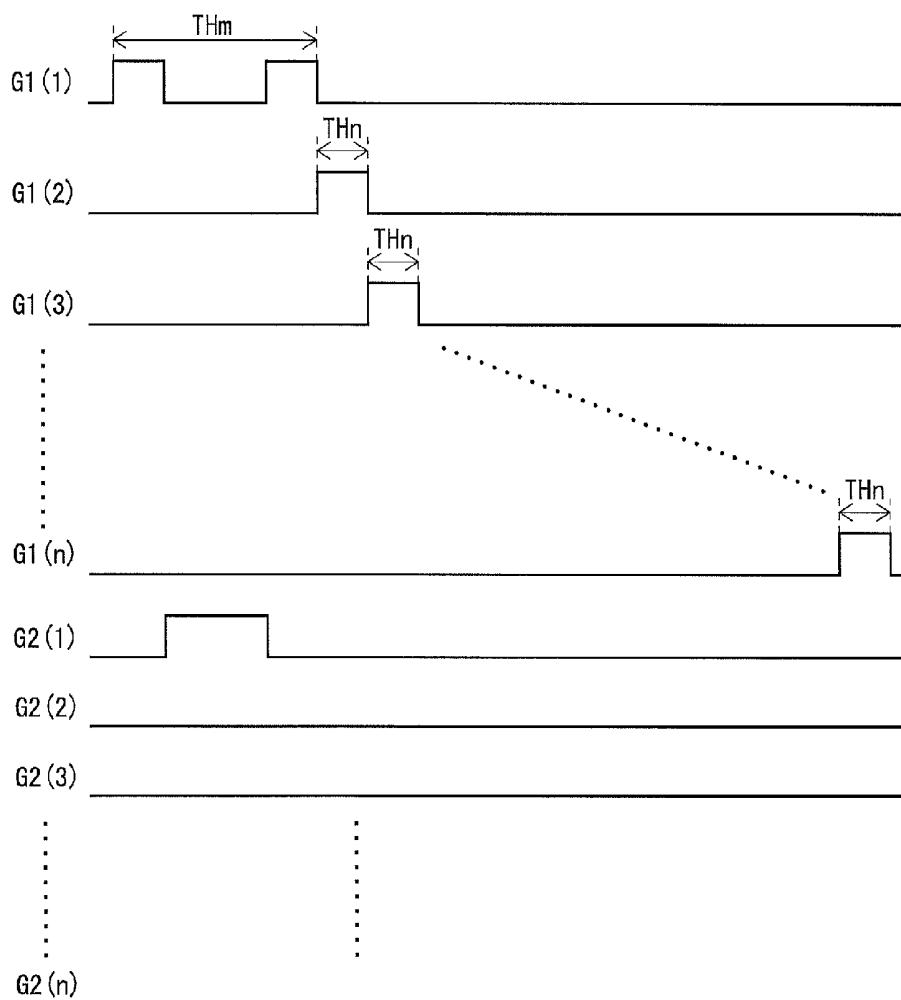

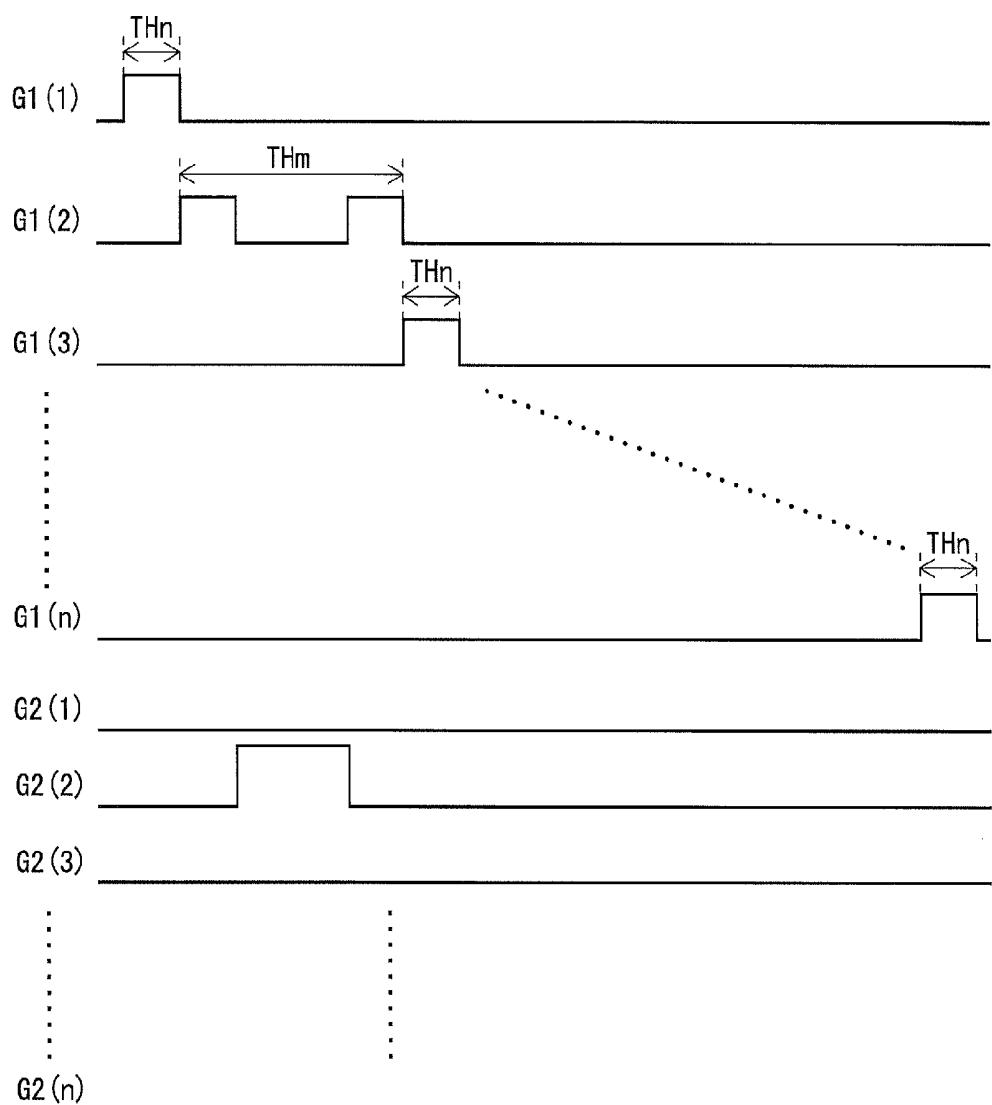

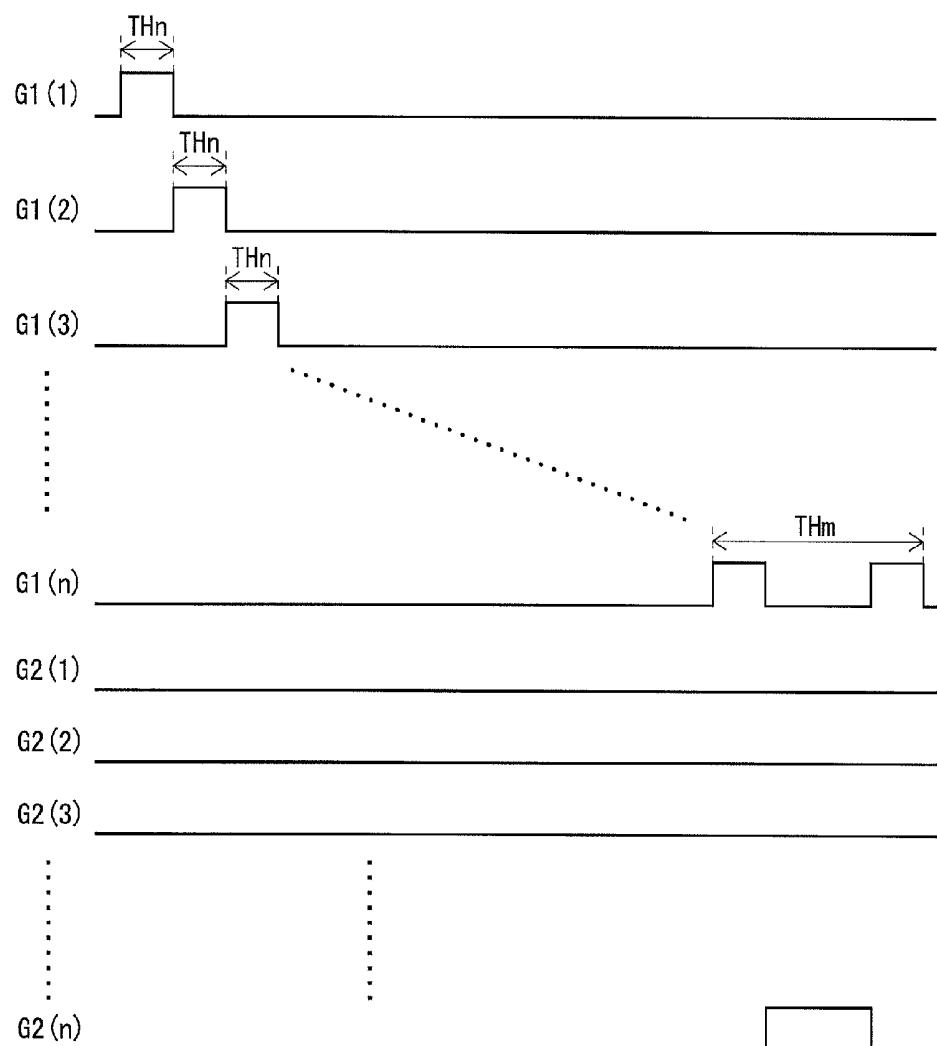

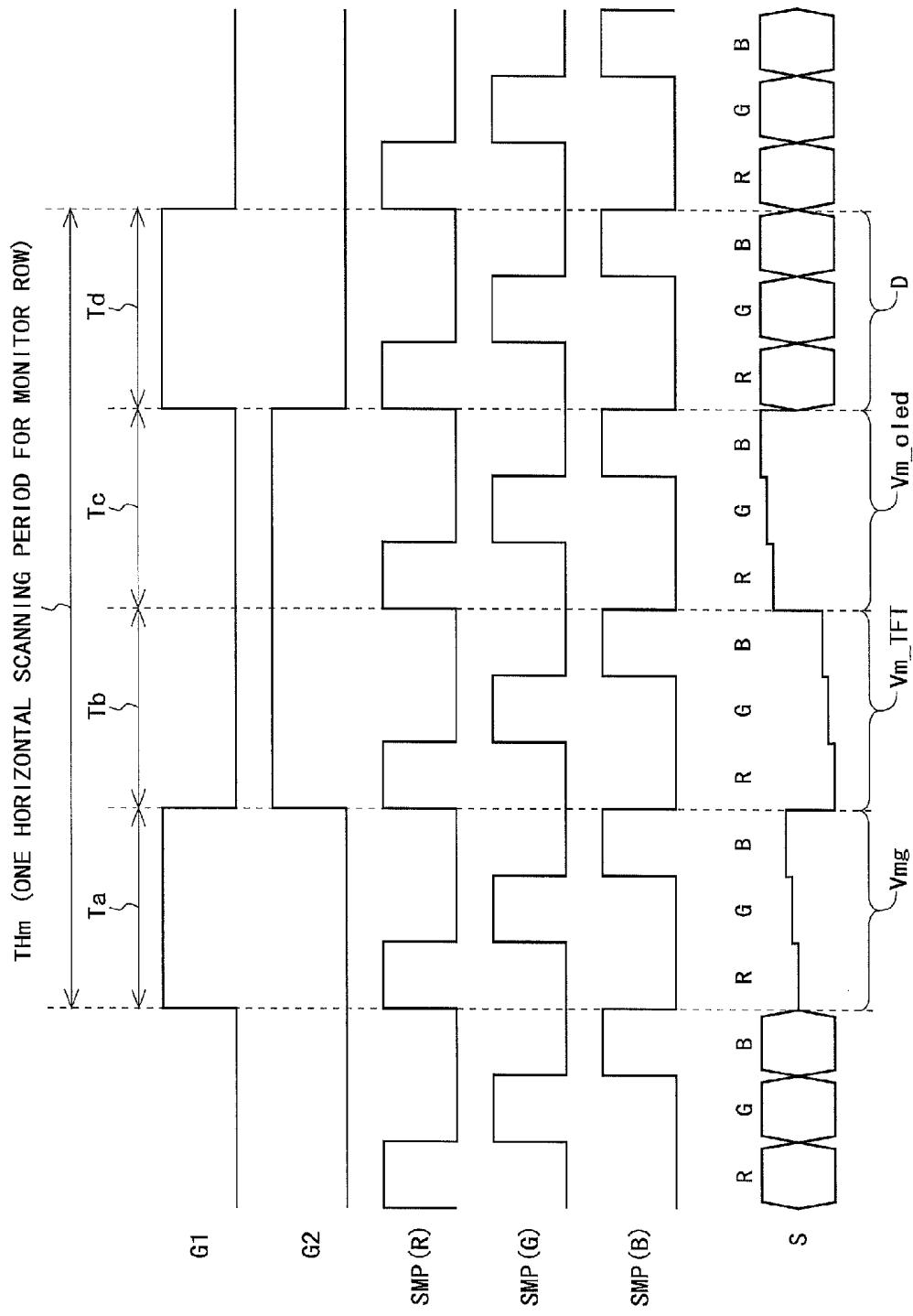

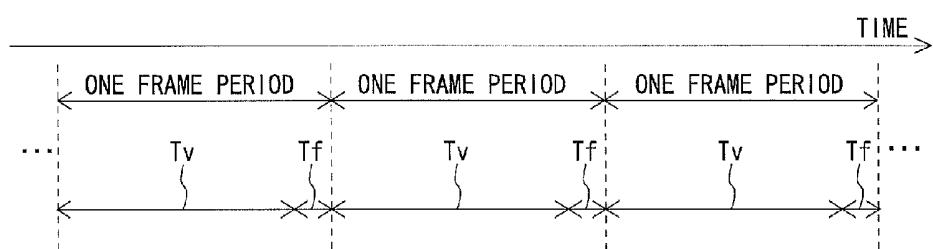

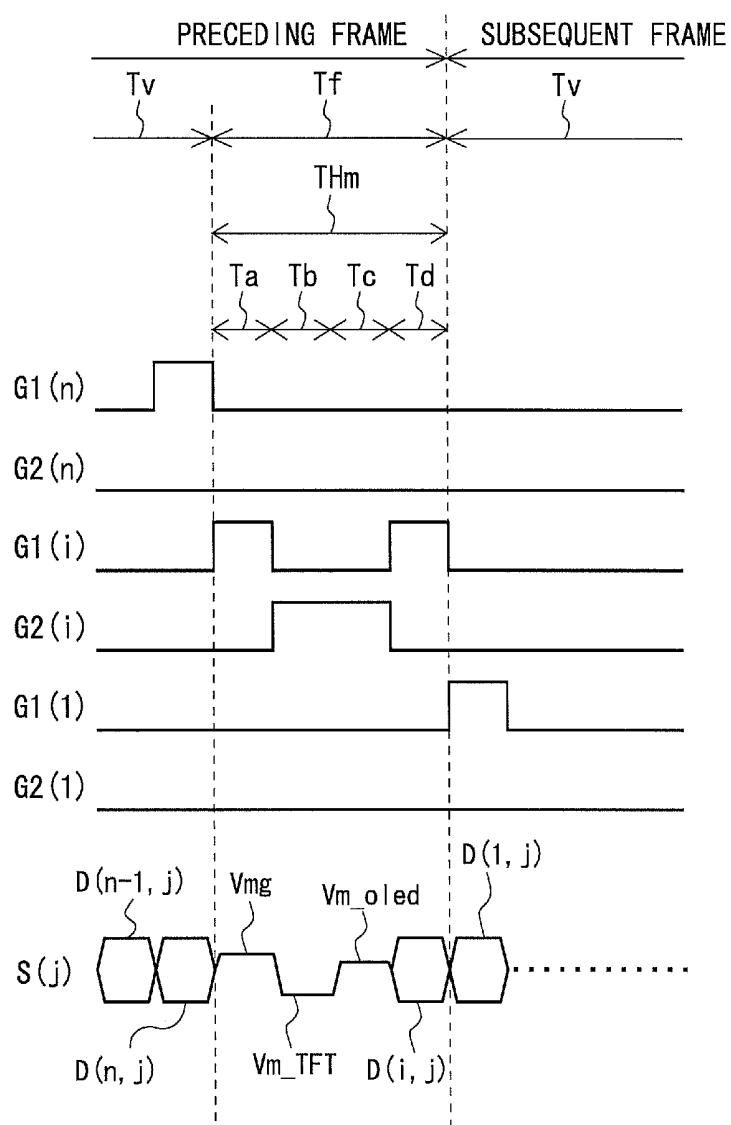

[0111] FIG. 3 is a timing chart for explaining operations of a gate driver in the embodiment.

[0112] FIG. 4 is a timing chart for explaining the operations of the gate driver in the embodiment.

[0113] FIG. 5 is a timing chart for explaining the operations of the gate driver in the embodiment.

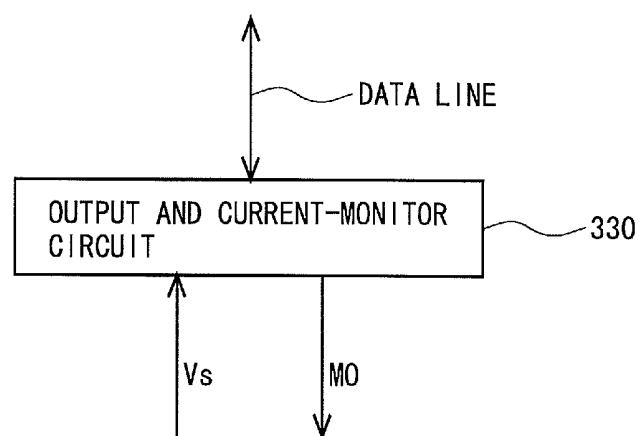

[0114] FIG. 6 is a diagram for explaining input-output signals of an output and current-monitor circuit in an output unit in the embodiment.

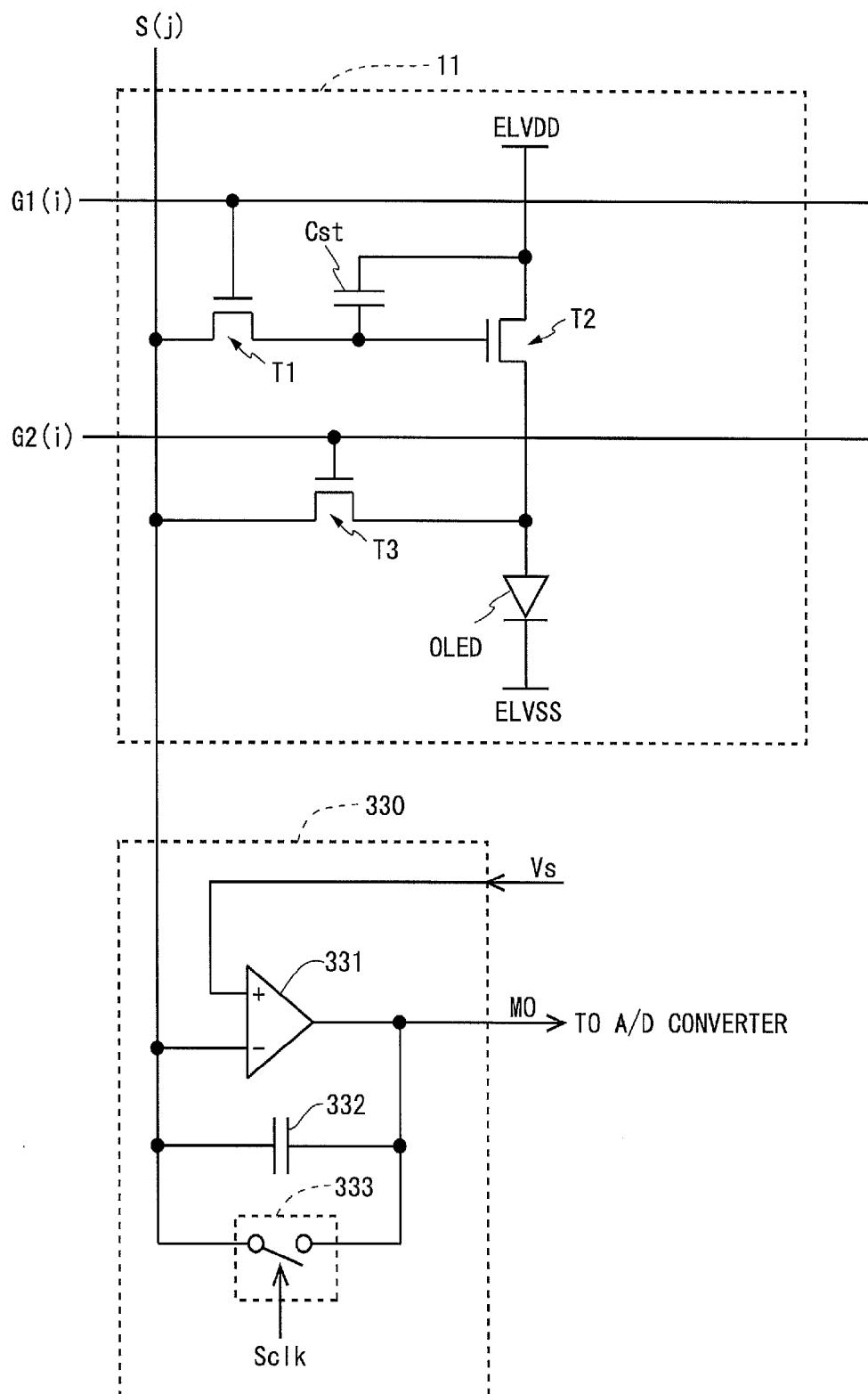

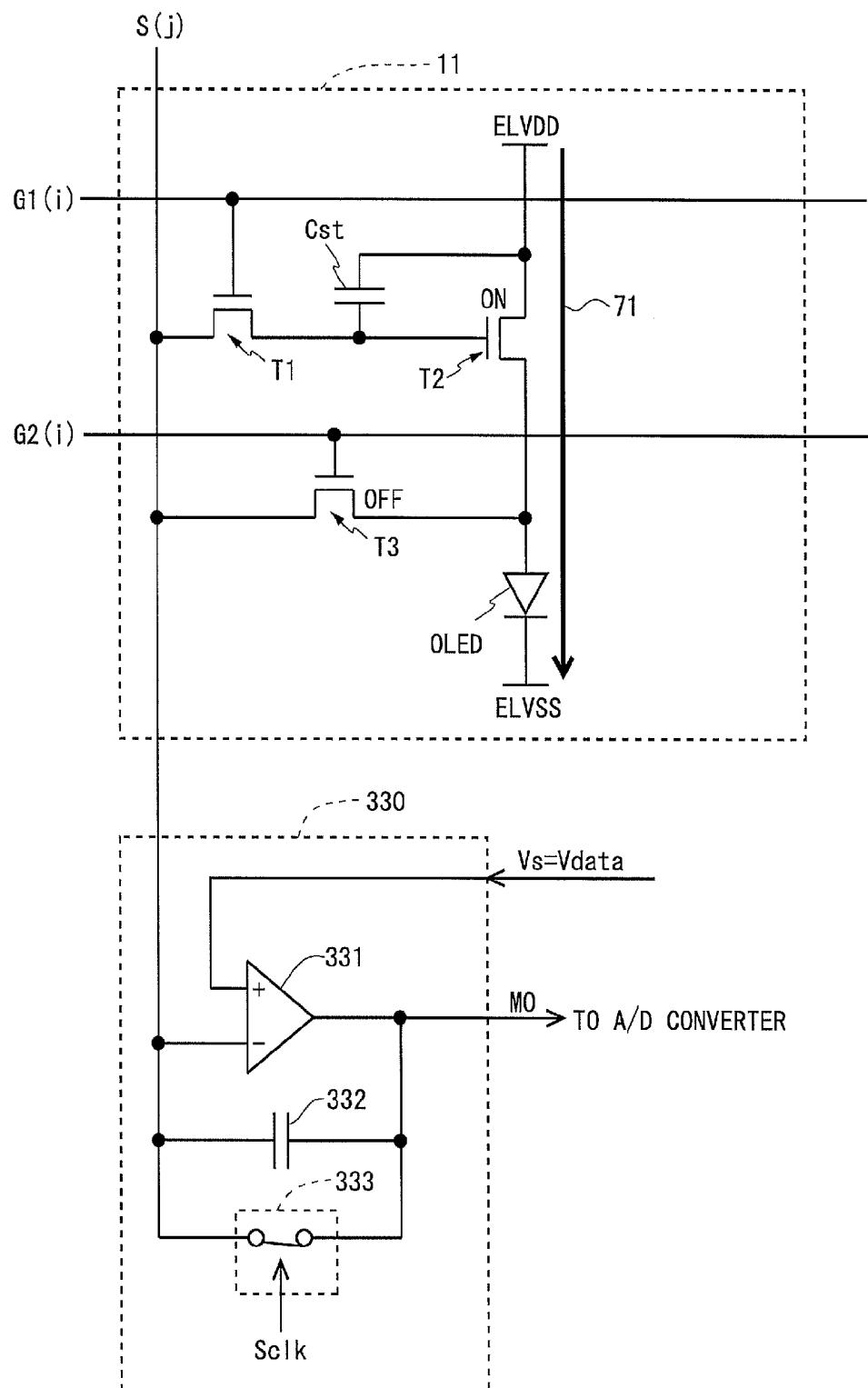

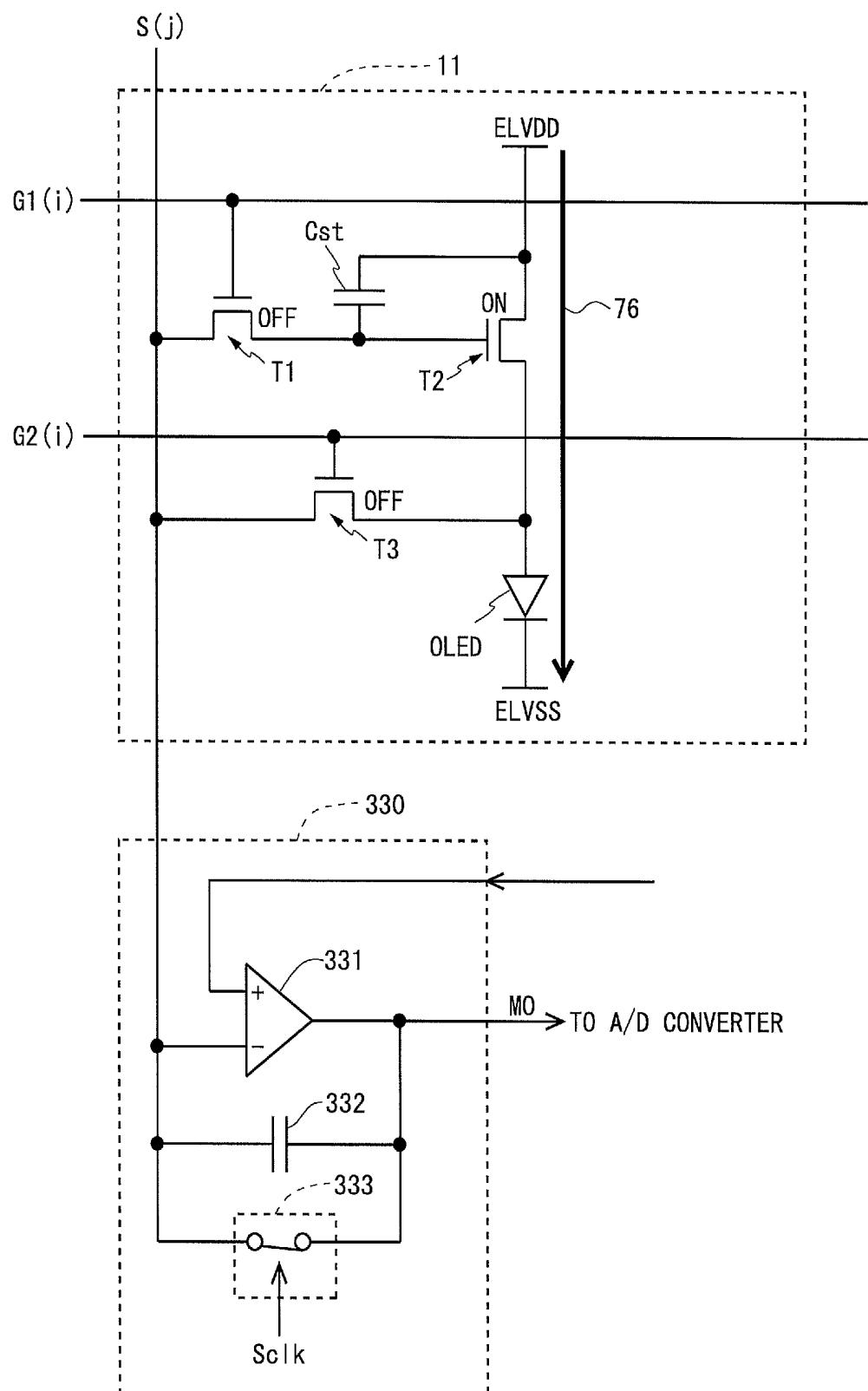

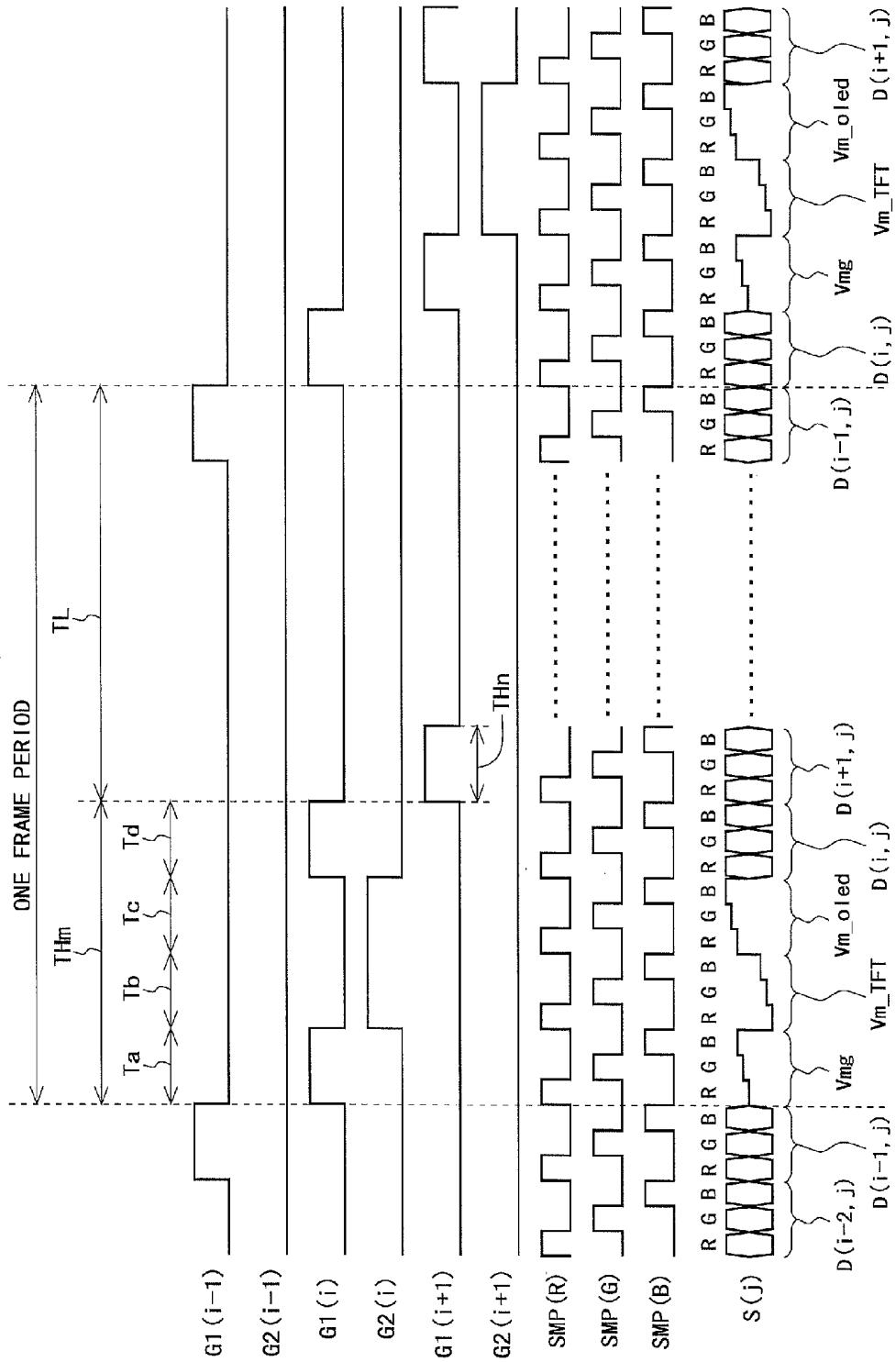

[0115] FIG. 7 is a circuit diagram showing configurations of a pixel circuit and the output and current-monitor circuit in the embodiment.

[0116] FIG. 8 is a table for explaining a transition of the operations in respective rows in the embodiment.

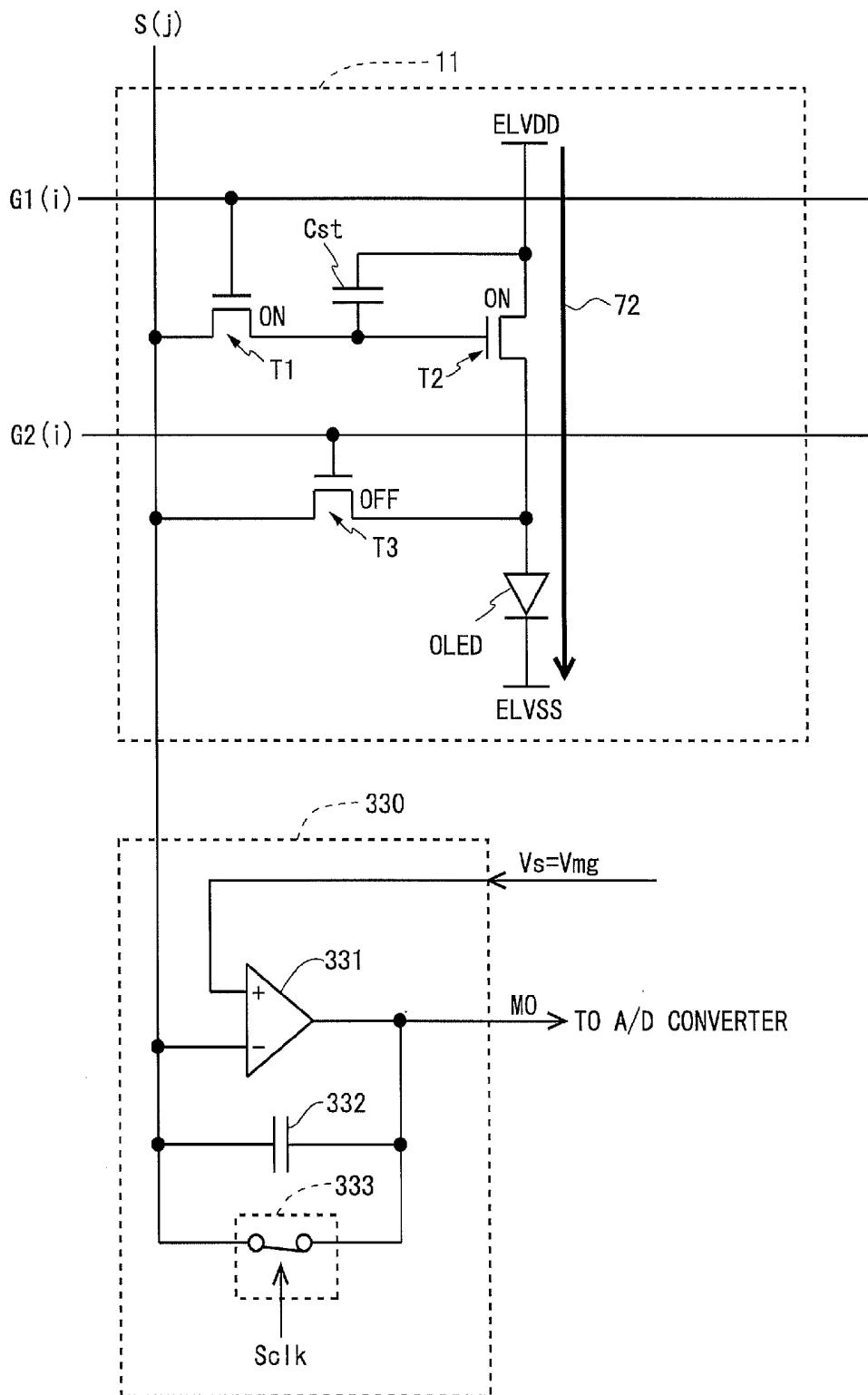

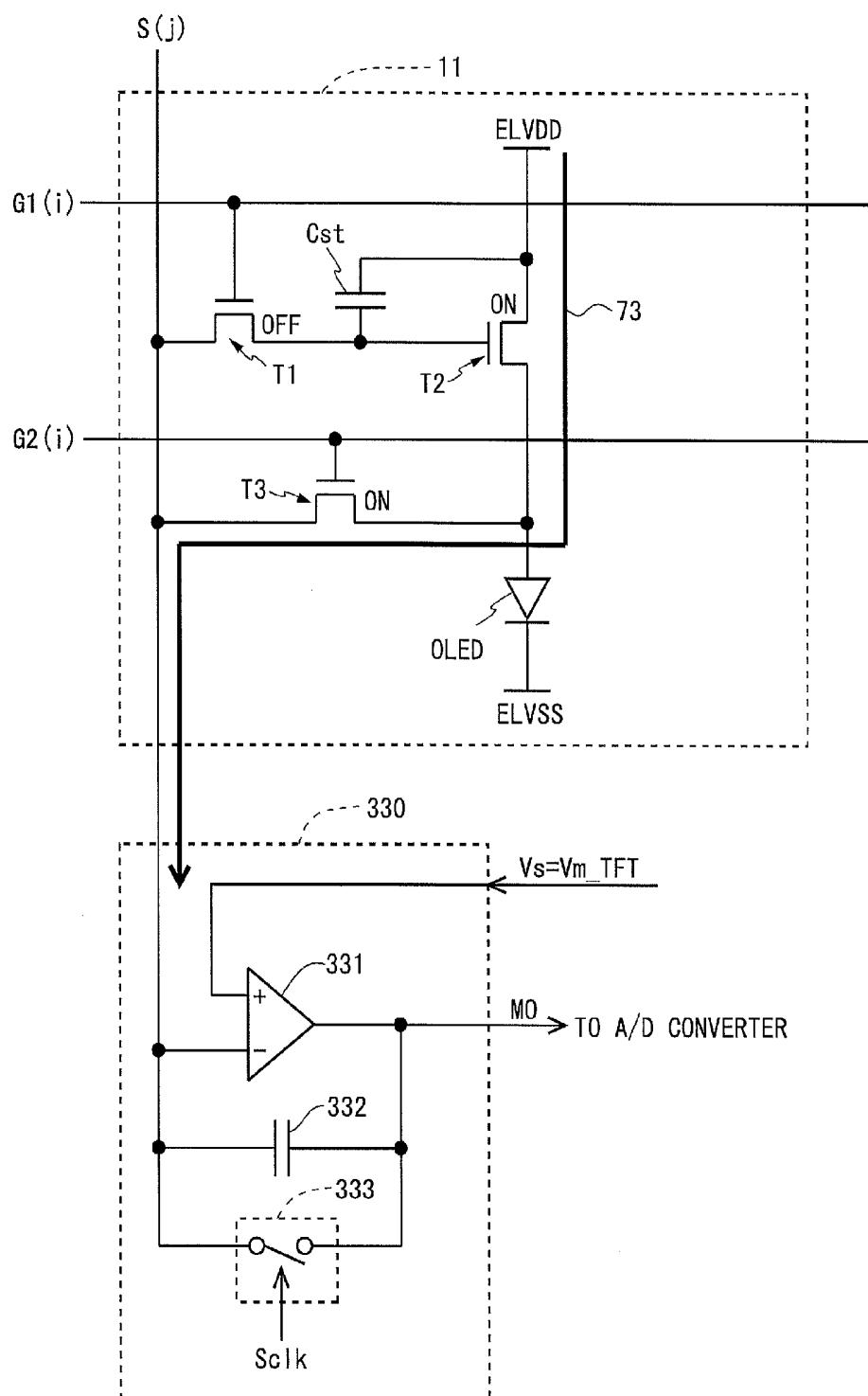

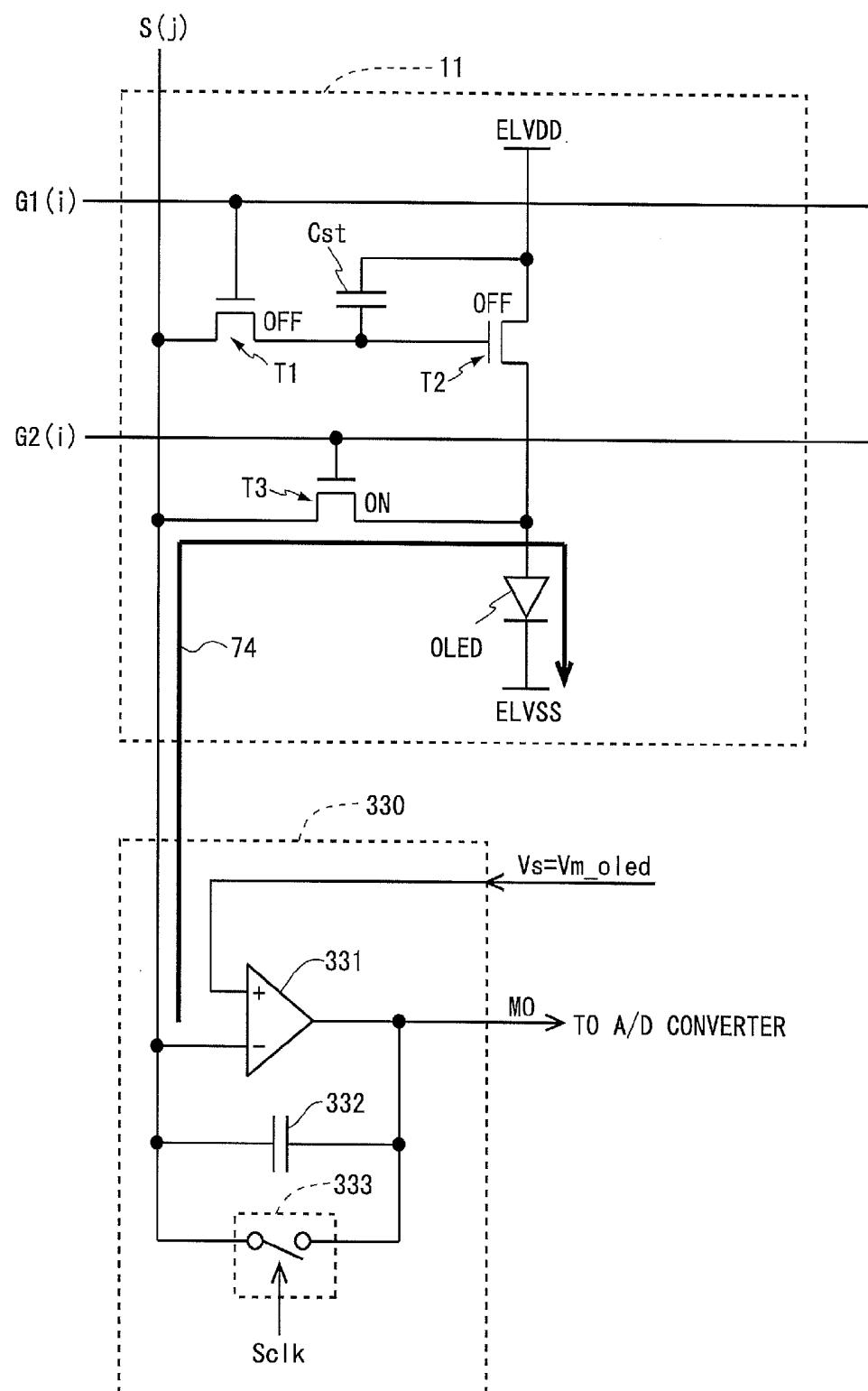

[0117] FIG. 9 is a diagram for explaining a flow of a current in an event where a usual operation is performed in the embodiment.

[0118] FIG. 10 is a timing chart for explaining operations of a pixel circuit (a pixel circuit on an i-th row and a j-th column) included in the monitor row in the embodiment.

[0119] FIG. 11 is a diagram for explaining a flow of the current in a detection preparation period in the embodiment.

[0120] FIG. 12 is a diagram for explaining a flow of the current in a TFT characteristic detection period in the embodiment.

[0121] FIG. 13 is a diagram for explaining a flow of the current in an OLED characteristic detection period in the embodiment.

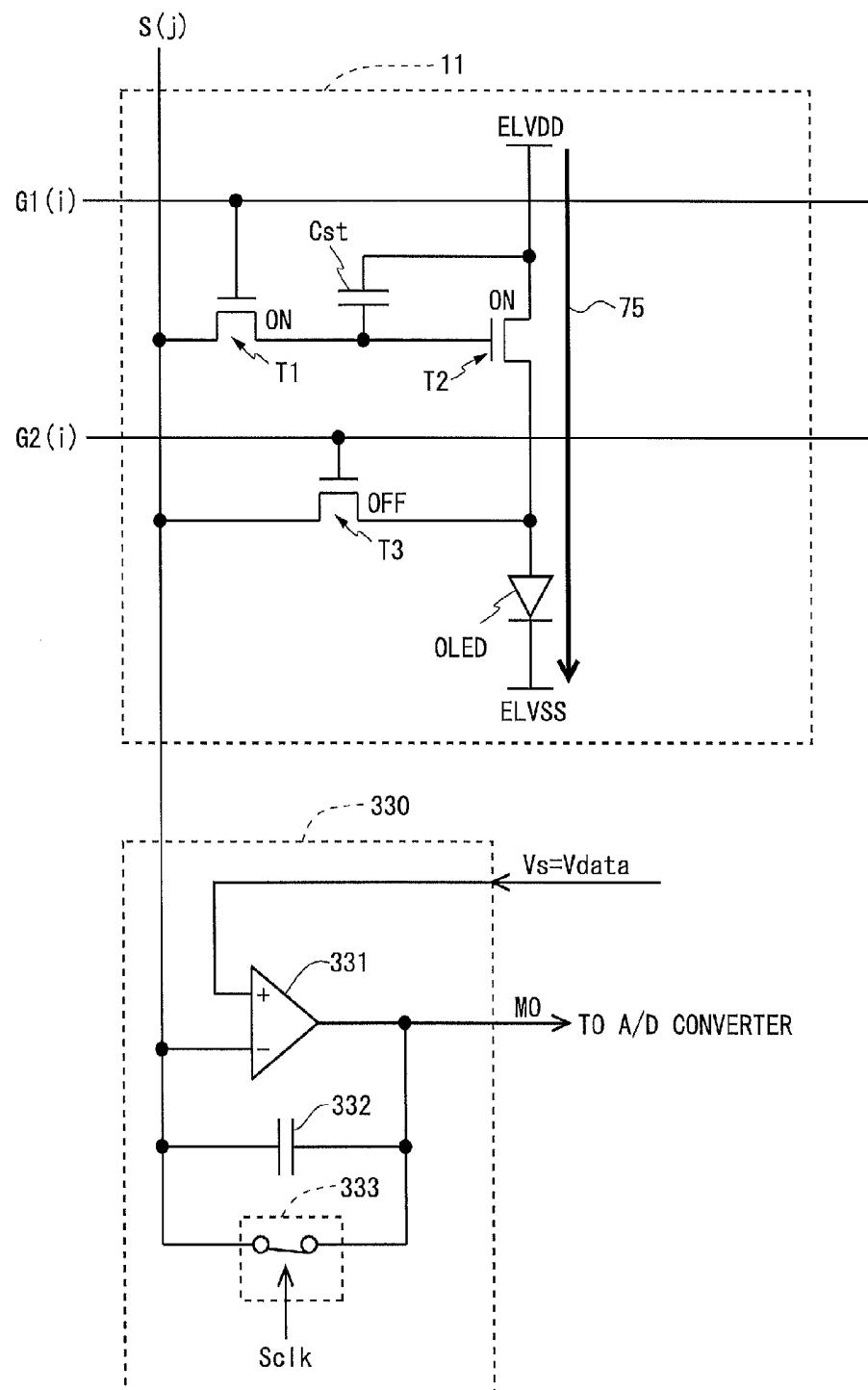

[0122] FIG. 14 is a diagram for explaining a flow of the current in a light emission preparation period in the embodiment.

[0123] FIG. 15 is a diagram for explaining a flow of the current in a light emission period in the embodiment.

[0124] FIG. 16 is a diagram of comparing one frame period in the monitor row and one frame period in a non-monitor row with each other in the embodiment.

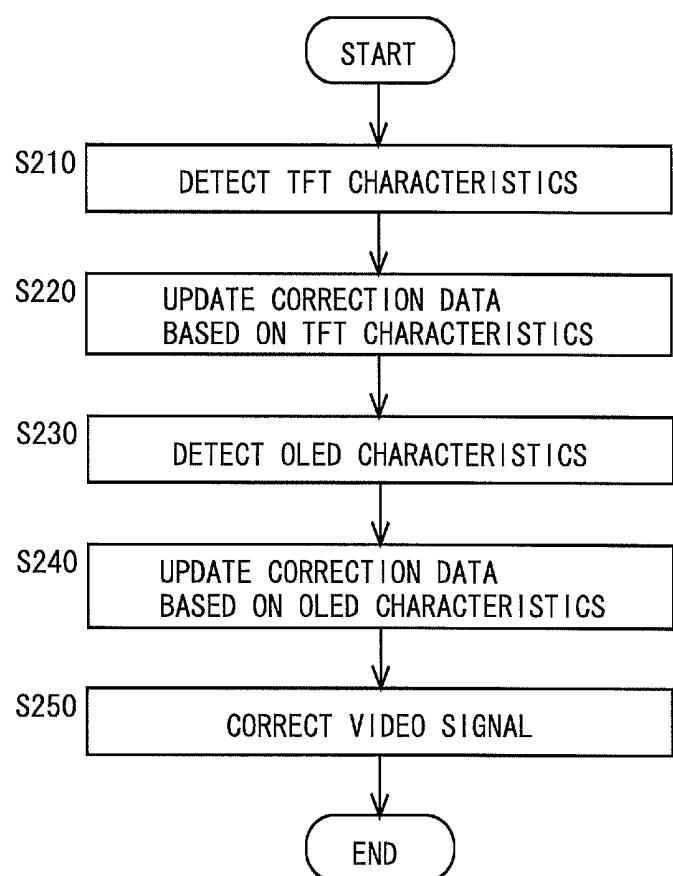

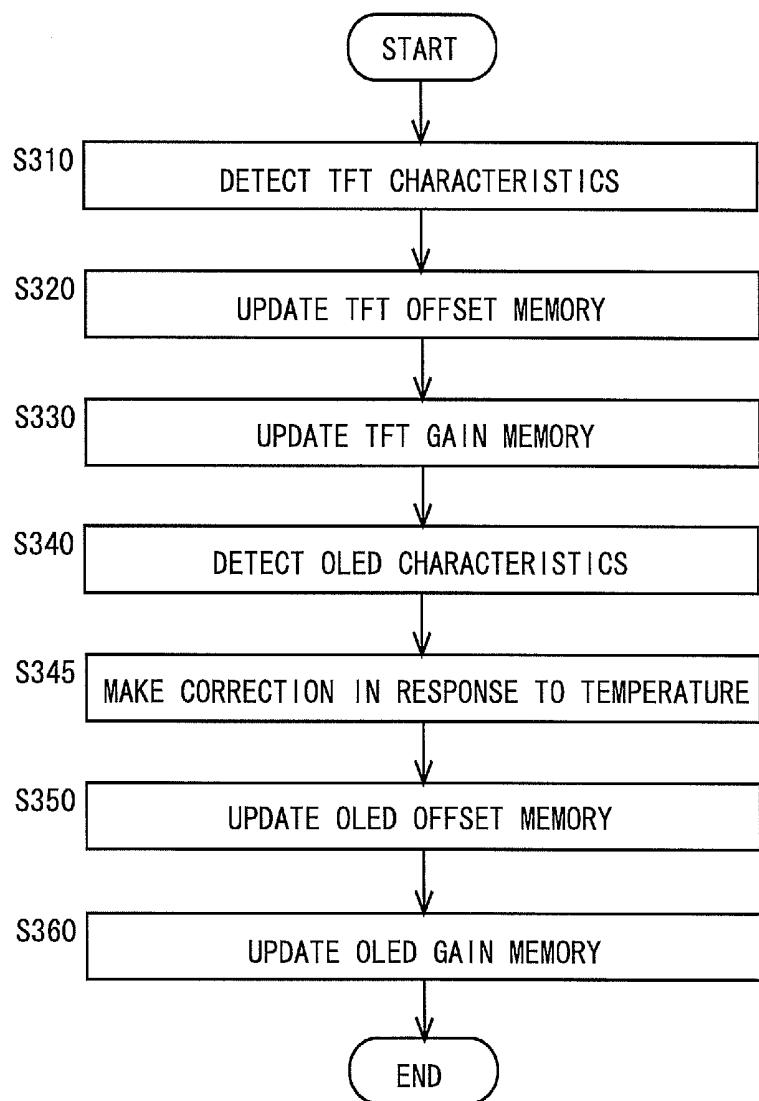

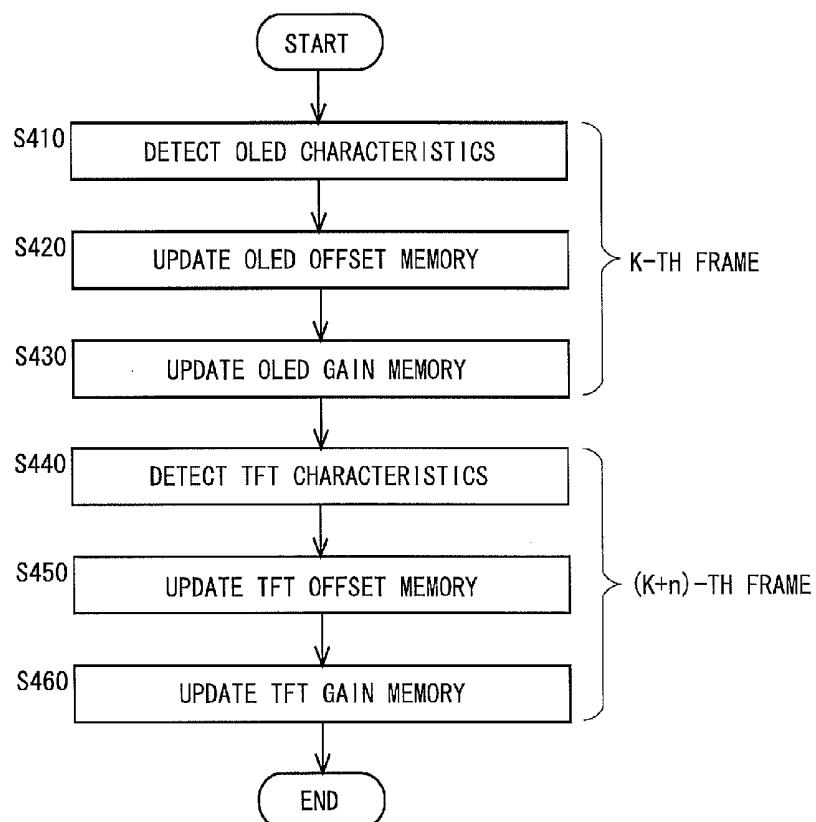

[0125] FIG. 17 is a flowchart for explaining a procedure of updating correction data in a correction data storage unit in the embodiment.

[0126] FIG. 18 is a diagram for explaining correction of a video signal in the embodiment.

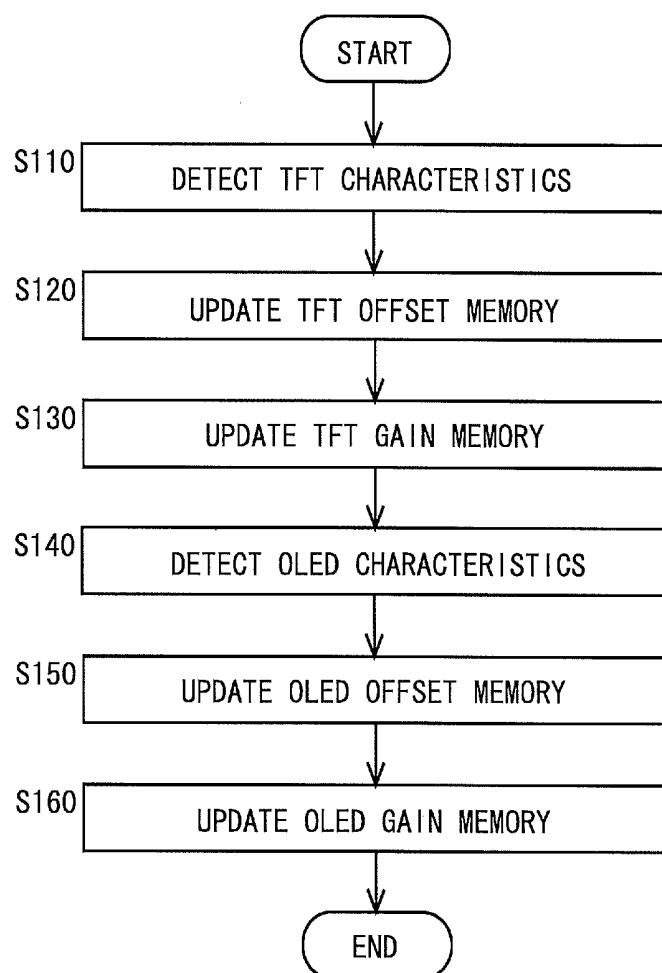

[0127] FIG. 19 is a flowchart for explaining an outline of operations related to detection of TFT characteristics and OLED characteristics in the embodiment.

[0128] FIG. 20 is a graph for explaining an effect in the embodiment.

[0129] FIG. 21 is a graph for explaining an effect in the embodiment.

[0130] FIG. 22 is a block diagram showing an overall configuration of an organic EL display device in a first modification example of the embodiment.

[0131] FIG. 23 is a diagram showing a detailed configuration of a connection control unit in the first modification example of the embodiment.

[0132] FIG. 24 is a timing chart for explaining details of one horizontal scanning period for a monitor row in the first modification example of the embodiment.

[0133] FIG. 25 is a timing chart for explaining operations of a pixel circuit 11 (defined to be a pixel circuit on an i-th row and a j-th column) included in a monitor row in the first modification example of the embodiment.

[0134] FIG. 26 is a block diagram showing an overall configuration of an organic EL display device in a second modification example of the embodiment.

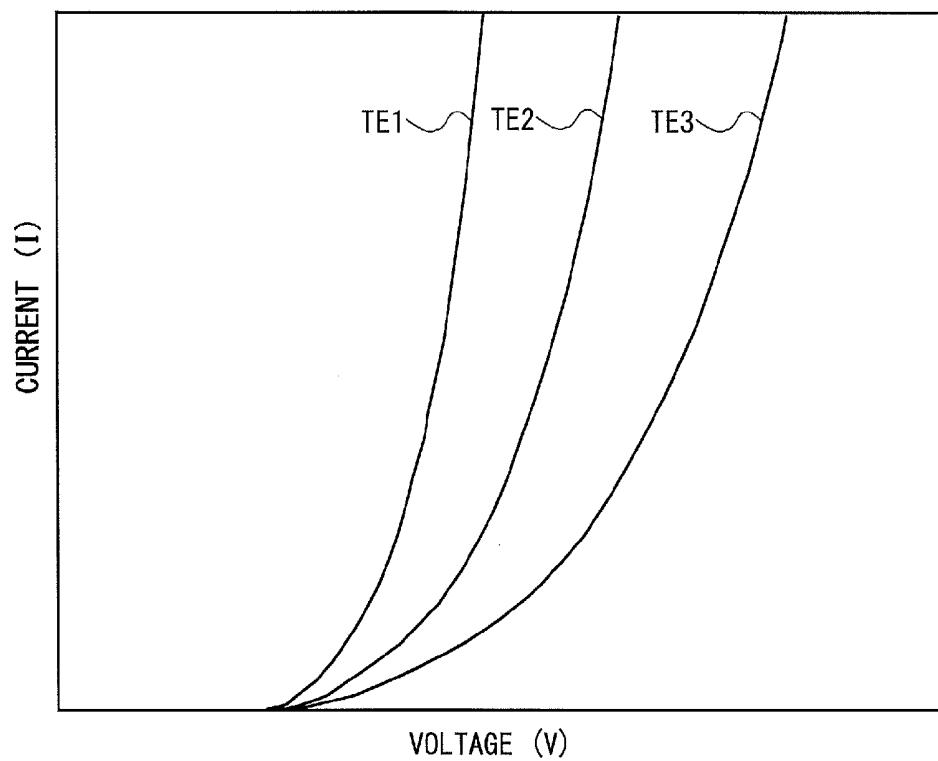

[0135] FIG. 27 is a graph for explaining temperature dependency of current-voltage characteristics of the organic EL element.

[0136] FIG. 28 is a block diagram showing an overall configuration of an organic EL display device in a third modification example of the embodiment.

[0137] FIG. 29 is a flowchart for explaining a procedure of updating correction data in a correction data storage unit in the third modification example of the embodiment.

[0138] FIG. 30 is a table for explaining a transition of operations in respective rows in a fourth modification example of the embodiment.

[0139] FIG. 31 is a timing chart for explaining details of one horizontal scanning period for a monitor row (that is, a timing chart in a frame in which an OLED characteristic detection operation is performed in the monitor row) in the fourth modification example of the embodiment.

[0140] FIG. 32 is a timing chart for explaining details of one horizontal scanning period for the monitor row (that is, a timing chart in a frame in which a TFT characteristic detection operation is performed in the monitor row) in the fourth modification example of the embodiment.

[0141] FIG. 33 is a flowchart for explaining a procedure of updating correction data in a correction data storage unit in the fourth modification example of the embodiment.

[0142] FIG. 34 is a diagram for explaining a configuration of one frame period.

[0143] FIG. 35 is a timing chart for explaining operations of a pixel circuit (defined to be a pixel circuit on an i-th row and a j-th column) included in a monitor row during a vertical retrace line period in a fifth modification example of the embodiment.

[0144] FIG. 36 is a timing chart for explaining operations of the pixel circuit (defined to be a pixel circuit on an i-th row and a j-th column) included in the monitor row during one frame period in the fifth modification example of the embodiment.

[0145] FIG. 37 is a circuit diagram showing a configuration of a conventional general pixel circuit.

[0146] FIG. 38 is a timing chart for explaining operations of the pixel circuit shown in FIG. 37.

[0147] FIG. 39 is a graph for explaining a case where no compensation is made for a deterioration of a drive transistor and a deterioration of an organic EL element.

[0148] FIG. 40 is a graph for explaining a case where the compensation is made only for the deterioration of the drive transistor.

#### MODES FOR CARRYING OUT THE INVENTION

[0149] A description is made below of an embodiment of the present invention while referring to the accompanying drawings. Note that, in the following, it is assumed that m and n are integers of 2 or more, that i is an integer of 1 or more to n or less, and that j is an integer of 1 or more to m or less. Moreover, in the following, characteristics of a drive transistor provided in a pixel circuit are referred to as “TFT characteristics”, and characteristics of an organic EL element provided in the pixel circuit are referred to as “OLED characteristics”.

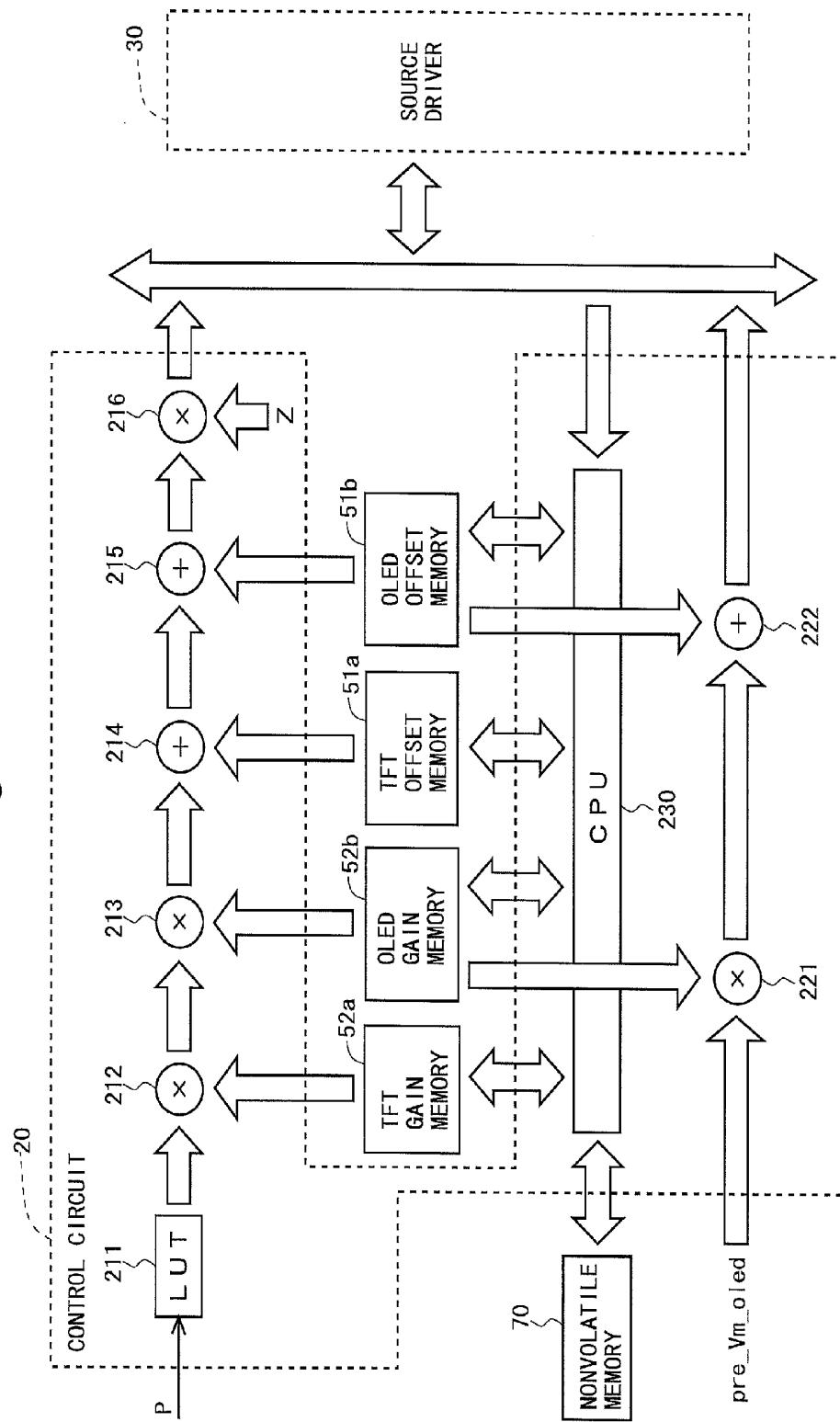

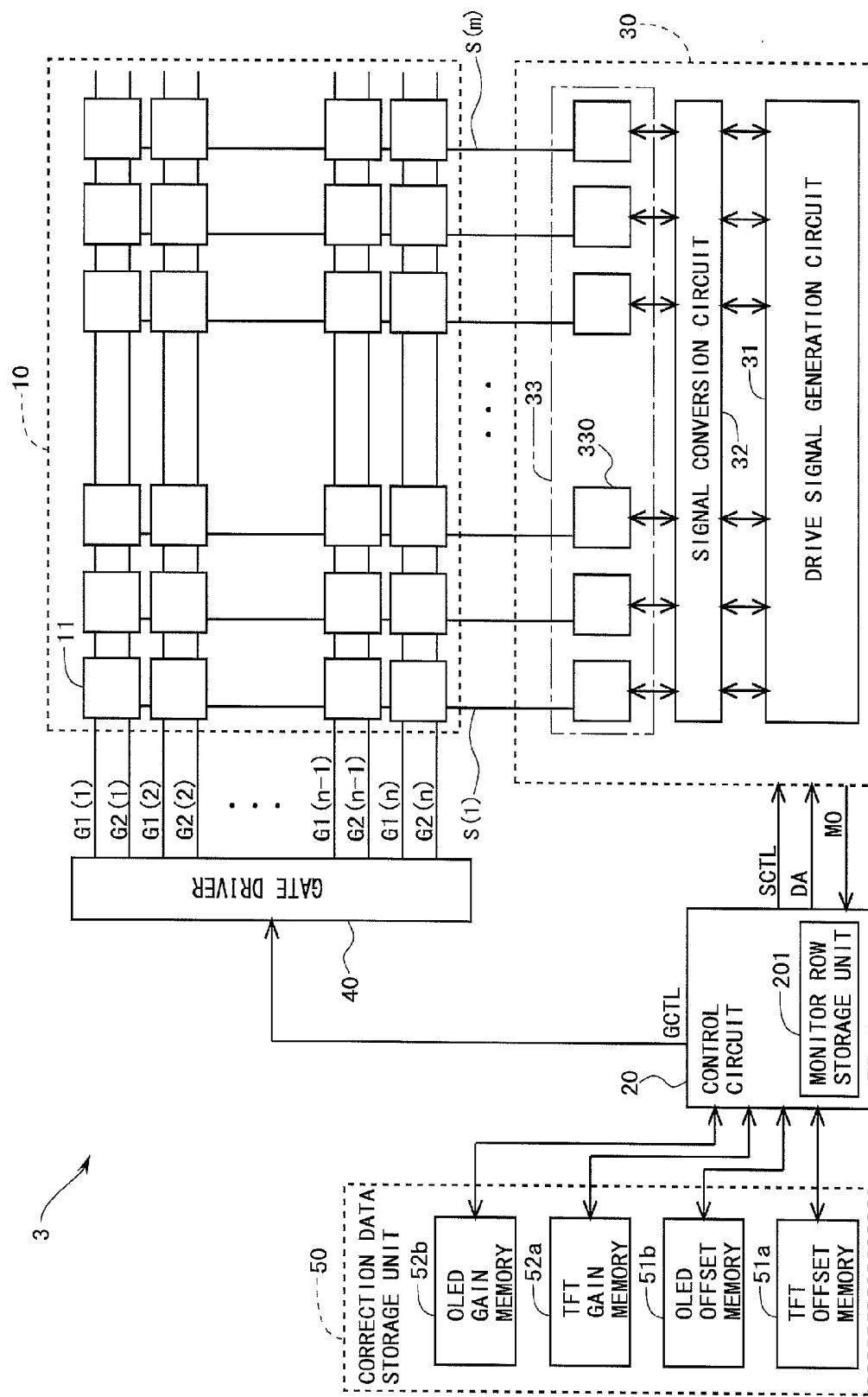

#### 1. OVERALL CONFIGURATION

[0150] FIG. 2 is a block diagram showing an overall configuration of an active matrix-type organic EL display device 1 according to an embodiment of the present invention. This organic EL display device 1 includes: a display unit 10; a control circuit 20; a source driver (a data line drive circuit) 30; a gate driver (a scanning line drive circuit) 40; and a correction data storage unit 50. In this embodiment, a pixel circuit drive unit is realized by the source driver 30 and the gate driver 40. Note that a configuration in which either one or both of the source driver 30 and the gate driver 40 are formed integrally with the display unit 10 may be adopted.

[0151] In the display unit 10, m pieces of data lines S(1) to S(m) and n pieces of scanning lines G1(1) to G1(n) perpendicular thereto are arranged. In the following, an extending direction of the data lines is defined as a Y-direction, and an extending direction of the scanning lines is defined as an X-direction. Constituents which go along the Y-direction are sometimes referred to as “columns”, and constituents which go along the X-direction are sometimes referred to as “rows”. Moreover, in the display unit 10, n pieces of monitor control lines G2(1) to G2(n) are arranged so as to correspond to the n pieces of scanning lines G1(1) to G1(n) in a one-to-one relationship. The scanning lines G1(1) to G1(n) and the monitor control lines G2(1) to G2(n) are parallel to each other. Moreover, in the display unit 10, n\*m pieces of pixel circuits 11 are provided so as to correspond to crossing points of the n pieces of scanning lines G1(1) to G1(n) and the m pieces of data lines S(1) to S(m). The n\*m pieces of pixel circuits 11 are provided as described above, whereby a pixel matrix with n rows and m columns is formed in the display unit 10. Moreover, in the display unit 10, there are arranged: high-level power supply lines which supply a high-level power supply voltage; and low-level power supply lines which supply a low-level power supply voltage.

[0152] Note that, in the following, in a case where it is not necessary to distinguish the m pieces of data lines S(1) to S(m) from one another, the data lines are simply denoted by reference symbol S. In a similar way, in a case where it is not necessary to distinguish the n pieces of scanning lines G1(1) to G1(n) from one another, the scanning lines are simply denoted by reference symbol G1, and in a case where it is not necessary to distinguish the n pieces of monitor control lines G2(1) to G2(n) from one another, the monitor control lines are simply denoted by reference symbol G2.

[0153] The data lines S in this embodiment are not only used as signal lines which transfer brightness signals for allowing organic EL elements in the pixel circuits 11 to emit light at desired brightness, but are also used as signal lines for giving the pixel circuits 11 control potentials for detecting TFT characteristics and OLED characteristics and as signal lines which become routes of currents indicating the TFT characteristics and the OLED characteristics and being measurable by output and current-monitor circuits 330 to be described later.

[0154] The control circuit 20 controls operations of the source driver 30 by giving a data signal DA and a source control signal SCTL to the source driver 30, and controls operations of the gate driver 40 by giving a gate control signal GCTL to the gate driver 40. The source control signal SCTL

includes, for example, a source start pulse, a source clock, and a latch strobe signal. The gate control signal GCTL includes, for example, a gate start pulse, a gate clock and an output enable signal. Moreover, the control circuit 20 receives monitor data MO given from the source driver 30, and updates correction data stored in the correction data storage unit 50. Note that the monitor data MO is data measured in order to obtain the TFT characteristics and the OLED characteristics.

[0155] The gate driver 40 is connected to the n pieces of scanning lines G1(1) to G1(n) and the n pieces of monitor control lines G2(1) to G2(n). The gate driver 40 is composed of a shift register, a logic circuit and the like. Incidentally, in the organic EL display device 1 according to this embodiment, a video signal (data serving as an origin of the above-described data signal DA), which is sent from an outside, is corrected based on the TFT characteristics and the OLED characteristics. With regard to this, in this embodiment, in each of frames, detection of the TFT characteristics and the OLED characteristics is performed for one row. That is to say, when the detection of the TFT characteristics and the OLED characteristics for a first row is performed in a certain frame, detection of the TFT characteristics and the OLED characteristics for a second row is performed in a next frame, and detection of the TFT characteristics and the OLED characteristics for a third row is performed in a frame next to the next frame. In such a way, during an n frame period, detection of the TFT characteristics and the OLED characteristics for n rows is performed. Note that, in this description, a row for which the detection of the TFT characteristics and the OLED characteristics is performed at a time of focusing on any frame is referred to as a "monitor row", and rows other than the monitor row are referred to as "non-monitor rows".

[0156] Here, when the frame in which the detection of the TFT characteristics and the OLED characteristics for the first row is performed is defined as a (k+1)-th frame, then the n pieces of scanning lines G1(1) to G1(n) and the n pieces of monitor control lines G2(1) to G2(n) are driven as shown in FIG. 3 in the (k+1)-th frame, are driven as shown in FIG. 4 in a (k+2)-th frame, and are driven as shown in FIG. 5 in a (k+n)-th frame. Note that, with regard to FIG. 3 to FIG. 5, a high-level state is an active state. Moreover, in FIG. 3 to FIG. 5, one horizontal scanning period for the monitor row is denoted by reference symbol THm, and one horizontal scanning period for each of the non-monitor rows is denoted by reference symbol THn.

[0157] As grasped from FIG. 3 to FIG. 5, a length of one horizontal scanning period differs between the monitor row and the non-monitor row. Specifically, a length of one horizontal scanning period for the monitor row is four times a length of one horizontal scanning period for the non-monitor row. However, the present invention is not limited to this. With regard to the non-monitor row, there is one selection period during one frame period in a similar way to a general display device. With regard to the monitor row, there are two selection periods during one frame period unlike the general display device. A first selection period is a first one-fourth period in the one horizontal scanning period THm, and a second selection period is a last one-fourth period in the one horizontal scanning period THm. Note that a more detailed description of the one horizontal scanning period THm for the monitor row will be made later.

[0158] As shown in FIG. 3 to FIG. 5, in each of the frames, the monitor control lines G2 corresponding to the non-monitor rows are maintained in an inactive state. The monitor

control line G2 corresponding to the monitor row is maintained in an active state during a period other than the selection period in the one horizontal scanning period THm (that is, a period while the scanning line G1 is in the inactive state). In this embodiment, the gate driver 40 is configured so that the n pieces of scanning lines G1(1) to G1(n) and the n pieces of monitor control lines G2(1) to G2(n) can be driven in such a way as described above. Note that, in order to generate two pulses in the scanning line G1 during one frame period in the monitor row, a waveform of the output enable signal sent from the control circuit 20 to the gate driver 40 just needs to be controlled by using a method known in public.

[0159] The source driver 30 is connected to the m pieces of data lines S(1) to S(m). The source driver 30 is composed of: a drive signal generation circuit 31; a signal conversion circuit 32; and an output unit 33 made of m pieces of output and current-monitor circuits 330. The m pieces of output and current-monitor circuits 330 in the output unit 33 are individually connected to the corresponding data lines S among the m pieces of data lines S(1) to S(m).

[0160] The drive signal generation circuit 31 includes a shift register, a sampling circuit and a latch circuit. In the drive signal generation circuit 31, the shift register sequentially transfers the source start pulse from an input end to an output end in synchronization with the source clock. In response to this transfer of the source start pulse, sampling pulses corresponding to the respective data lines S are outputted to the data lines S from the shift register. The sampling circuit sequentially stores such data signals DA, which are equivalent to one row, in accordance with timing of the sampling pulses. The latch circuit captures and holds the data signals DA for one row which are stored in the sampling circuit, in response to the latch strobe signal.

[0161] Note that, in this embodiment, each of the data signals DA includes: a brightness signal for allowing the organic EL element of each pixel to emit light at desired brightness; and a monitor control signal for controlling the operations of the pixel circuit 11 in an event of detecting the TFT characteristics and the OLED characteristics.

[0162] The signal conversion circuit 32 includes: a D/A converter and an A/D converter. The data signals DA for one row which are held in the latch circuit in the drive signal generation circuit 31 as mentioned above, are converted into analog voltages by the D/A converter in the signal conversion circuit 32. The analog voltages thus converted are given to the output and current-monitor circuits 330 in the output unit 33. Moreover, the signal conversion circuit 32 is given monitor data MO from the output and current-monitor circuits 330 in the output unit 33. The monitor data MO are converted from the analog voltages into digital signals in the A/D converter in the signal conversion circuit 32. Then, the monitor data MO converted into the digital signals are given to the control circuit 20 via the drive signal generation circuit 31.

[0163] FIG. 6 is a diagram for explaining input-output signals of the output and current-monitor circuit 330 in the output unit 33. Each of the output and current-monitor circuits 330 is given an along voltage Vs as the data signal DA from the signal conversion circuit 32. The analog voltage Vs is applied to the data line S via a buffer in the output and current-monitor circuit 330. Moreover, the output and current-monitor circuit 330 has a function to measure the current flowing through the data line S. Data measured by the output and current-monitor circuit 330 is given as the monitor data MO to the signal conversion circuit 32. Note that a detailed

configuration of the output and current-monitor circuit 330 will be described later (refer to FIG. 7).

[0164] The correction data storage unit 50 includes: a TFT offset memory 51a; an OLED offset memory 51b; a TFT gain memory 52a; and an OLED gain memory 52b. Note that these four memories may be a physically single memory, or maybe physically different memories. The correction data storage unit 50 stores the correction data for use in correcting the video signal sent from the outside. Specifically, the TFT offset memory 51a stores an offset value, which is based on a detection result of the TFT characteristics, as the correction data. The OLED offset memory 51b stores an offset value, which is based on a detection result of the OLED characteristics, as the correction data. The TFT gain memory 52a stores a gain value, which is based on a detection result of the TFT characteristics, as the correction data. The OLED gain memory 52b stores a deterioration correction coefficient, which is based on a detection result of the OLED characteristics, as the correction data. Note that, typically, such offset values, the number of which is equal to the number of pixels in the display unit 10, and such gain values, the number of which is equal thereto, are stored as the correction data, which are based on the detection results of the TFT characteristics, in the TFT offset memory 51a and the TFT gain memory 52a, respectively. Moreover, typically, such offset values, the number of which is equal to the number of pixels in the display unit 10, and such deterioration correction coefficients, the number of which is equal thereto, are stored as the correction data, which are based on the detection results of the OLED characteristics, in the OLED offset memory 51b and the OLED gain memory 52b, respectively. However, in each of the memories, a single value may be stored for each unit of a plurality of the pixels.

[0165] Based on the monitor data MO given from the source driver 30, the control circuit 20 updates the offset values in the TFT offset memory 51a, the offset values in the OLED offset memory 51b, the gain values in the TFT gain memory 52a and the deterioration correction coefficients in the OLED gain memory 52b. Moreover, the control circuit 20 reads out the offset values in the TFT offset memory 51a, the offset values in the OLED offset memory 51b, the gain values in the TFT gain memory 52a and the deterioration correction coefficients in the OLED gain memory 52b, and corrects the video signal. Data obtained by the correction is sent as the data signal DA to the source driver 30.

## 2. CONFIGURATIONS OF PIXEL CIRCUIT AND OUTPUT AND CURRENT-MONITOR CIRCUIT

[0166] <2.1 Pixel Circuit>

[0167] FIG. 7 is a circuit diagram showing configurations of the pixel circuit 11 and the output and current-monitor circuit 330. Note that the pixel circuit 11 shown in FIG. 7 is the pixel circuit 11 on the i-th row and the j-th column. This pixel circuit 11 includes: one organic EL element OLED; three transistors T1 to T3; and one capacitor Cst. The transistor T1 functions as an input transistor that selects the pixel, the transistor T2 functions as a drive transistor that controls the supply of the current to the organic EL element OLED, and the transistor T3 functions as a monitor control transistor that controls whether or not to detect the TFT characteristics and the OLED characteristics.

[0168] The transistor T1 is provided between the data line S(j) and a gate terminal of the transistor T2. With regard to the transistor T1, a gate terminal thereof is connected to the

scanning line G1(i), and a source terminal thereof is connected to the data line S(j). The transistor T2 is provided in series to the organic EL element OLED. With regard to the transistor T2, a gate terminal thereof is connected to a drain terminal of the transistor T1, a drain terminal thereof is connected to the high-level power supply line ELVDD, and a source terminal thereof is connected to the anode terminal of the organic EL element OLED. With regard to the transistor T3, a gate terminal thereof is connected to the monitor control line G2(i), a drain terminal thereof is connected to the anode terminal of the organic EL element OLED, and a source terminal thereof is connected to the data line S(j). With regard to the capacitor Cst, one end thereof is connected to the gate terminal of the transistor T2, and other end thereof is connected to the drain terminal of the transistor T2. Note that a first capacitor is realized by this capacitor Cst. A cathode terminal of the organic EL element OLED is connected to the low-level power supply line ELVSS.

[0169] Incidentally, in the configuration shown in FIG. 37, the capacitor Cst has been provided between the gate and source of the transistor T2. In contrast, in this embodiment, the capacitor Cst is provided between the gate and drain of the transistor T2. A reason for this is as follows. In this embodiment, during one frame period, a control to vary a potential of the data line S(j) in a state where the transistor T3 is turned ON is performed. Supposing that the capacitor Cst is provided between the gate and source of the transistor T2, then a gate potential of the transistor T2 also varies in response to the variation of the potential of the data line S(j). Then, there can occur a matter that an ON/OFF state of the transistor T2 does not become a desired state. Accordingly, in this embodiment, in order that the gate potential of the transistor T2 cannot vary in response to the variation of the potential of the data line S(j), the capacitor Cst is provided between the gate and drain of the transistor T2 as shown in FIG. 7. However, in a case where an influence given from the variation of the potential of the data line S(j) to the gate potential of the transistor T2 is small, the capacitor Cst may be provided between the gate and source of the transistor T2.

[0170] <2.2 Regarding Transistor in Pixel Circuit>

[0171] In this embodiment, all of the transistors T1 to T3 in the pixel circuit 11 are of the n-channel type. Moreover, in this embodiment, for the transistors T1 to T3, oxide TFTs (thin film transistors using an oxide semiconductor for channel layers) are adopted.

[0172] A description is made below of an oxide semiconductor layer included in each of the oxide TFTs. The oxide semiconductor layer is, for example, an In—Ga—Zn—O-based semiconductor layer. The oxide semiconductor layer contains, for example, an In—Ga—Zn—O-based semiconductor. The In—Ga—Zn—O-based semiconductor is a ternary oxide of In (indium), Ga (gallium) and Zn (zinc). A ratio (composition ratio) of In, Ga and Zn is not particularly limited. For example, the composition ratio may be In:Ga:Zn=2:2:1, In:Ga:Zn=1:1:1, In:Ga:Zn=1:1:2, and the like.

[0173] Such a TFT including the In—Ga—Zn—O-based semiconductor layer has high mobility (mobility exceeding 20 times that of an amorphous silicon TFT) and a low leak current (leak current of less than  $1/100$  of that of the amorphous silicon TFT). Accordingly, this TFT is suitably used as a drive TFT (the above-described transistor T2) in the pixel circuit and a switching TFT (the above-described transistor T1) therein. When the TFT including the In—Ga—Zn—O-based

semiconductor layer is used, electric power consumption of the display device can be reduced to a great extent.

[0174] The In—Ga—Zn—O-based semiconductor may be amorphous, or may include a crystalline portion and have crystallinity. As the crystalline In—Ga—Zn—O-based semiconductor, a crystalline In—Ga—Zn—O-based semiconductor, in which a c-axis is oriented substantially perpendicularly to a layer surface, is preferable. A crystal structure of the In—Ga—Zn—O-based semiconductor as described above is disclosed, for example, in Japanese Patent Application Laid-Open No. 2012-134475.

[0175] The oxide semiconductor layer may contain other oxide semiconductors in place of the In—Ga—Zn—O-based semiconductor. For example, the oxide semiconductor layer may contain a Zn—O-based semiconductor (ZnO), an In—Zn—O-based semiconductor (IZO (registered trademark)), a Zn—Ti—O-based semiconductor (ZTO), a Cd—Ge—O-based semiconductor, a Cd—Pb—O-based semiconductor, a CdO (cadmium oxide), a Mg—Zn—O-based semiconductor, an In—Sn—Zn—O-based semiconductor (for example,  $In_2O_3—SnO_2—ZnO$ ), an In—Ga—Sn—O-based semiconductor and the like.

[0176] <2.3 Output and Current-Monitor Circuit>

[0177] While referring to FIG. 7, a description is made of a detailed configuration of the output and current-monitor circuit 330 in this embodiment. This output and current-monitor circuit 330 includes an operational amplifier 331, a capacitor 332 and a switch 333. Note that a second capacitor is realized by the capacitor 332. With regard to the operational amplifier 331, an inverting input terminal thereof is connected to the data line S(j), and a non-inverting input terminal thereof is given the analog voltage Vs as the data signal DA. The capacitor 332 and the switch 333 are provided between an output terminal of the operational amplifier 331 and the data line S(j). As described above, this output and current-monitor circuit 330 is composed of an integrating circuit. In such a configuration, when the switch 333 is turned to an ON state by a control clock signal Sclk, an output terminal of the operational amplifier 331 and the inverting input terminal thereof turn to a short circuit state. In such a way, potentials of the output terminal of the operational amplifier 331 and the data line S(j) become equal to a potential of the analog voltage Vs. In an event where the current flowing through the data line S(j) is measured, the switch 333 is turned to an OFF state by the control clock signal Sclk. In such a way, due to the presence of the capacitor 332, the potential of the output terminal of the operational amplifier 331 changes in response to a magnitude of the current flowing through the data line S(j). An output from the operational amplifier 331 is sent as the monitor data MO to the A/D converter in the signal conversion circuit 32.

### 3. DRIVE METHOD

[0178] <3.1 Outline>

[0179] Next, a description is made of a drive method in this embodiment. As mentioned above, in this embodiment, in each of frames, the detection of the TFT characteristics and the OLED characteristics is performed for one row. In each frame, an operation for performing the detection of the TFT characteristics and the OLED characteristics (hereinafter, referred to as a “characteristic detection operation”) is performed for the monitor row, and a usual operation is performed for the non-monitor row. That is to say, when the frame in which the detection of the TFT characteristics and

the OLED characteristics for the first row is performed is defined as the (k+1)-th frame, then the operations in the respective rows change as shown in FIG. 8. Moreover, when the detection of the TFT characteristics and the OLED characteristics is performed, the correction data in the correction data storage unit 50 is updated by using a detection result thereof. Then, the video signal is corrected by using the correction data stored in the correction data storage unit 50.

[0180] FIG. 1 is a timing chart for explaining details of one horizontal scanning period THm for the monitor row. Note that a characteristic detection processing period is realized by this one horizontal scanning period THm. As shown in FIG. 1, the one horizontal scanning period THm for the monitor row is composed of: a period (hereinafter referred to as a “detection preparation period”) Ta where preparation for detecting the TFT characteristics and the OLED characteristics is performed in the monitor row; a period (hereinafter referred to as a “TFT characteristic detection period”) Tb where current measurement for detecting the TFT characteristics is performed; a period (hereinafter referred to as an “OLED characteristic detection period”) Tc where current measurement for detecting the OLED characteristics is performed; and a period (hereinafter referred to as a “light emission preparation period) Td where preparation for allowing the organic EL element OLED to emit light is performed in the monitor row. Note that, in this embodiment, a current measurement period is realized by the TFT characteristic detection period and the OLED characteristic detection period.

[0181] During the detection preparation period Ta, the scanning line G1 is set to an active state, the monitor control line G2 is set to an inactive state, and the data line S is given a potential Vmg. During the TFT characteristic detection period Tb, the scanning line G1 is set to the inactive state, the monitor control line G2 is set to the active state, and the data line S is given a potential Vm\_TFT. During the OLED characteristic detection period Tc, the scanning line G1 is set to the inactive state, the monitor control line G2 is set to the active state, and the data line S is given a potential Vm\_oled. During the light emission preparation period Td, the scanning line G1 is set to the active state, the monitor control line G2 is set to the inactive state, and the data line S is given a data potential D corresponding to a target brightness of the organic EL element OLED included in the monitor row. In this embodiment, a first predetermined potential is realized by the potential Vmg, and a second predetermined potential is realized by the potential Vm\_TFT and the potential Vm\_oled. Note that the potential Vmg, the potential Vm\_TFT and the potential Vm\_oled will be described later in detail.

[0182] <3.2 Operations of Pixel Circuit>

[0183] <3.2.1 Usual Operation>

[0184] In each frame, the usual operation is performed in the non-monitor row. In the pixel circuit 11 included in the non-monitor row, after writing that is based on the data potential Vdata corresponding to the target brightness is performed in the selection period, the transistor T1 is maintained in the OFF state. The transistor T2 turns to the ON state by the writing that is based on the data potential Vdata. The transistor T3 is maintained in the OFF state. Thus, as shown by an arrow denoted by reference numeral 71 in FIG. 9, a drive current is supplied to the organic EL element OLED via the transistor T2. In such a way, the organic EL element OLED emits light with brightness in accordance with the drive current.

[0185] <3.2.2 Characteristic Detection Operation>

[0186] In each frame, the characteristic detection operation is performed in the monitor row. FIG. 10 is a timing chart for explaining operations of the pixel circuit 11 (defined to be a pixel circuit 11 on the i-th row and the j-th column) included in the monitor row. Note that, in FIG. 10, the “one frame period” is shown while taking, as a reference, a starting point of time for a first selection period of the i-th row in the frame in which the i-th row is defined as the monitor row. Moreover, here, a period other than the above-mentioned one horizontal scanning period THm in the one frame period in the monitor row is referred to as a “light emission period”. Reference symbol TL is assigned to the light emission period.

[0187] In the detection preparation period Ta, the scanning line G1(i) is set to the active state, and the monitor control line G2(i) is maintained in the inactive state. Thus, the transistor T1 becomes the ON state, and the transistor T3 is maintained in the OFF state. Moreover, in this period, the data line S(j) is given the potential Vmg. By writing that is based on this potential Vmg, the capacitor Cst is charged, and the transistor T2 turns to the ON state. Accordingly, in the detection preparation period Ta, as shown by an arrow denoted by reference numeral 72 in FIG. 11, a drive current is supplied to the organic EL element OLED via the transistor T2. In such a way, the organic EL element OLED emits light with the brightness in accordance with the drive current. However, it is for an extremely short time that the organic EL element OLED emits light.

[0188] In the TFT characteristic detection period Tb, the scanning line G1(i) is set to the inactive state, and the monitor control line G2(i) is set to the active state. Thus, the transistor T1 becomes the OFF state, and the transistor T3 becomes the ON state. Moreover, in this period, the data line S(j) is given the potential Vm\_TFT. Note that, in the OLED characteristic detection period Tc to be described later, the data line S(j) is given the potential Vm\_oled. Moreover, as mentioned above, in the detection preparation period Ta, the writing that is based on the potential Vmg is performed.

[0189] Here, when a threshold voltage of the transistor T2, which is obtained based on the offset value stored in the TFT offset memory 51a, is defined as Vth(T2), a value of the potential Vmg, a value of the potential Vm\_TFT and a value of the potential Vm\_oled are set so that the following Expressions (1) and (2) are established.

$$Vm_{TFT} + Vth(T2) < Vmg \quad (1)$$

$$Vmg < Vm_{oled} + Vth(T2) \quad (2)$$

Moreover, when a light emission threshold voltage of the organic EL element OLED, which is obtained based on the offset value stored in the OLED offset memory 51b, is defined as Vth(oled), the value of the potential Vm\_TFT is set so that the following Expression (3) is established.

$$Vm_{TFT} < ELVSS + Vth(oled) \quad (3)$$

Moreover, when a breakdown voltage of the organic EL element OLED is defined as Vbr(oled), the value of the potential Vm\_TFT is set so that the following Expression (4) is established.